# 修士論文

# スーパーカミオカンデにおける 新データ収集エレクトロニクスの研究と開発

西野玄記

東京大学大学院理学系研究科物理学専攻 金行研究室

2006年1月

#### 論文要旨

大型水チェレンコフ検出器を用いたスーパーカミオカンデ実験では、これまでにも ニュートリノ振動や超新星爆発、陽子崩壊などに関して物理的に重要な結果が数多く 得られている。しかし、さらなる高精度な観測、低エネルギー領域、高エネルギー領 域への観測可能領域の拡大のためには、現在のエレクトロニクスではいくつかの問題 点があることが明らかになっている。そのため、我々は現在、新しいエレクトロニク スの開発を進めているところである。

本論文では、まず、新しいデータ収集エレクトロニクスの現段階での概念的なデザインを述べる。新しいエレクトロニクスの開発にあたって、大きな課題となるのは高精度な観測を実現するフロントエンドエレクトロニクス (ATM) と高速なデータ処理を実現するシステムである。システム全体の設計に関しては、現段階ではまだ多くの選択肢が残されているが、全てのチャンネルで 10 kHz のヒットが生じてもデッドタイム無く、処理することが可能なシステムを設計しつつある。

一方、新しい ATM の開発は具体的に進みつつある。本研究では、その中で中心的な役割を果たす時間電荷変換素子 (QTC) と AMT と呼ばれる TDC に関する評価を行った。特に、QTC に関しては我々が独自に ASIC として開発したものであり、そのプロトタイプの性能評価の全般が本研究の主要なテーマである。

QTC の性能評価では、電荷測定と時間測定の精度やダイナミックレンジといった基本性能に関しては、ほぼ我々の要請を満たすものができていることが分かった。また、現在問題となっているインピーダンスの整合に関しても QTC 自体ではほぼ 0.1% の反射係数を実現できるレベルにあることが分かった。さらに、温度依存性や線型性などの評価も行い、どのように補正を行えば良いかの考察も行った。これらの評価の結果から次期版へ向けて改善するべき点を洗い出し、次期版の再設計を行った。

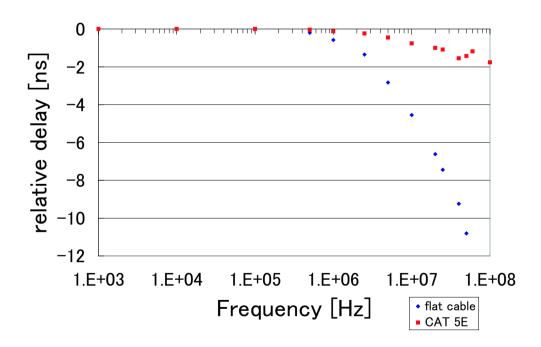

さらに、システム全体の基準となるクロックを発生させるモジュールの開発も行っている。クロックの分配に関しては分配のためのケーブルの評価を行い、40 m の距離をおいても 60 MHz の信号を伝送可能なケーブルを決定した。一方、クロック発生モジュールに関しては、回路設計を完了し、製作を順調に進めているところである。

# 目次

| 1 |      | 序論                                              | 1  |

|---|------|-------------------------------------------------|----|

|   | 1.1  | ニュートリノ振動                                        | 1  |

|   | 1.1. | 1 ニュートリノ振動                                      | 1  |

|   | 1.1. | 2 大気ニュートリノ                                      | 3  |

|   | 1.1. | 3 太陽二ュートリノ                                      | 6  |

|   | 1.2  | 超新星爆発ニュートリノ                                     | 9  |

|   | 1.3  | 新エレクトロニクス開発の動機                                  | 12 |

|   | 1.3. | 1 高エネルギー領域の観測可能領域の拡大                            | 13 |

|   | 1.3. | 2 低エネルギー領域の観測可能領域の拡大                            | 13 |

|   | 1.3. | 3 新エレクトロニクスへの要請のまとめ                             | 15 |

| 2 |      | スーパーカミオカンデ                                      | 16 |

| _ | 2.1  | 測定原理                                            |    |

|   | 2.1  | 検出器                                             |    |

|   | 2.3  | 光電子増倍管                                          |    |

|   | 2.4  | オンラインデータ収集系・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ |    |

|   | 2.5  | キャリブレーション                                       |    |

|   | 2.0  |                                                 | 1  |

| 3 |      | 現行のデータ収集エレクトロニクス                                | 23 |

|   | 3.1  | データ収集システムの概要                                    | 23 |

|   | 3.2  | 時間電荷測定モジュール (ATM)                               | 25 |

|   | 3.2. | 1 現在の ATM の特性のまとめ                               | 25 |

|   | 3.3  | SMP                                             | 26 |

|   | 3.4  | トリガーシステム                                        | 26 |

|   | 3.4. | 1 HITSUM                                        | 26 |

|   | 3.4. | 2 TRG                                           | 28 |

|   | 3.5  | 現在の ATM の問題点                                    | 28 |

| 4 |      | 新データ収集エレクトロニクスの概念設計                             | 33 |

|   | 4.1  | 新エレクトロニクスへの要請                                   | 33 |

|   | 4.1. | 1 フロントエンド (ATM) で解決すべき要請と解決策                    | 33 |

|   |      | 2 データ収集システム全体で解決すべき要請と解決策:高速化                   |    |

|   |      |                                                 |    |

|   | 4.2  | 新データ収集エレクトロニクスの全体図                              | 36 |

|   |      | 新データ収集エレクトロニクスの全体図                              |    |

| 4.       | 3 親        | f ATM                                                                            | 41         |

|----------|------------|----------------------------------------------------------------------------------|------------|

|          | 4.3.1      | 信号の流れ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                        | 41         |

|          | 4.3.2      | 信号入出力                                                                            | 42         |

|          | 4.3.3      | QTC の処理速度                                                                        | 45         |

|          | 4.3.4      | AMT (ATLAS Muon TDC)                                                             | 46         |

|          | 4.3.5      | データ量と処理速度                                                                        | 51         |

| 4.       | 4 <b>ラ</b> | ータ収集システム全体の高速化                                                                   | 55         |

|          | 4.4.1      | 新 SCH の開発と高速化 TKO プロトコル                                                          | 55         |

|          | 4.4.2      | イーサネット読み出しのための拡張ボード                                                              | 57         |

|          | 4.4.3      | 高速化に関するまとめ....................................                                   | 57         |

| 4.       | 5 h        | ・リガーシステム                                                                         | 59         |

|          | 4.5.1      | Forced Trigger                                                                   | 59         |

|          | 4.5.2      | Digital HITSUM                                                                   | 59         |

| _        | п-         |                                                                                  | <b>~</b> 1 |

| 5        |            | , , , , , , , , , , , , , , , , , , , ,                                          | 61         |

| 5.       |            | TC への要請と仕様の検討                                                                    |            |

|          |            | 電荷分解能とダイナミックレンジ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                              |            |

|          |            | 積分ゲート (Charge Gate) 時間と測定ゲート (Measure Gate) 時間: 処理速度 .                           |            |

|          |            | ディスクリミネータへの要請: 低ノイズ化                                                             |            |

|          |            |                                                                                  |            |

| 5.       |            | CAL 入力:キャリブレーション作業の簡素化                                                           |            |

| 5.       |            |                                                                                  |            |

| 5.<br>5. |            | TC の開発                                                                           |            |

|          |            | 基本性能の評価                                                                          |            |

|          |            | 評価基板                                                                             |            |

|          |            | 電荷測定ダイナミックレンジ                                                                    |            |

|          |            | 電荷測定精度                                                                           |            |

|          |            | 時間測定精度                                                                           |            |

|          |            | Time Walk: CFD の評価                                                               |            |

|          |            | インピーダンス整合                                                                        |            |

|          |            | クロストーク                                                                           |            |

|          |            |                                                                                  |            |

|          |            |                                                                                  | 92         |

| 5.       |            |                                                                                  | 94<br>95   |

|          |            | 「足性、緑空性、個体差に関する性能評価・・・・・・・・・・・・・・・・<br>温度依存性・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ |            |

|          |            |                                                                                  | 90         |

| 5.5  | .3 電荷線型性:単純な関数で記述できるか                                              |

|------|--------------------------------------------------------------------|

| 5.5  | .4 チャンネル間個体差                                                       |

| 5.5  | .5 キャリブレーション用入力 (CAL)                                              |

| 5.6  | 問題点と改善点:次期版への変更点102                                                |

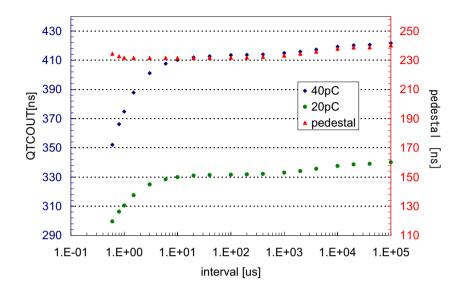

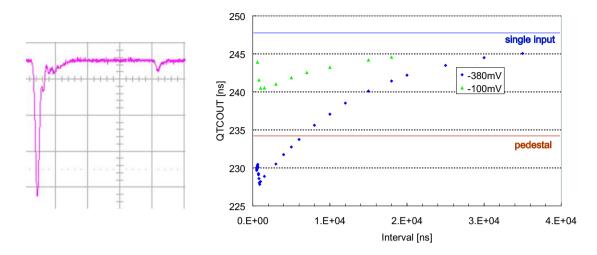

| 5.6  | .1 入力頻度依存性                                                         |

| 5.6  | .2 リセット中に入力された信号でヒットが生じる問題 $.$ $.$ $.$ $.$ $.$ $.$ $.$ $.$ $.$ $.$ |

| 5.6  | .3 微小な信号で動作が止まる問題                                                  |

| 5.7  | QTC 評価のまとめ                                                         |

| 6    | Master Clock Module (Mclock) の開発                                   |

| 6.1  | 60 MHz <b>のデータ転送のための検</b> 討                                        |

| 6.2  | 仕様                                                                 |

| 6.2  | .1 クロックの安定性への要請とクロックの選定                                            |

| 6.2  | .2 Master Clock Module の機能                                         |

| 6.3  | 開発経過                                                               |

| 7    | 結論 116                                                             |

| 付録 A | 現在の ATM の処理の詳細 117                                                 |

| A.1  | アナログ信号入力部                                                          |

| A.2  | AD 変換部                                                             |

| 付録 B | AMT の設定と読み書きタイミング 120                                              |

| B.1  | レジスタ設定                                                             |

| B.2  | 読み書きタイミング                                                          |

| B.2  | 2.1 CSR                                                            |

| R S  | 2.2 測定データ読み出し 129                                                  |

## 1 序論

スーパーカミオカンデは約 5 万トンの純水と約 13000 本の光電子増倍管からなる水チェレンコフ検出器であり、陽子崩壊の探索や太陽、大気、超新星爆発など様々な起源によるニュートリノの研究を目的として、1991 年に建設が開始され、1996 年 4 月に観測が開始された。また、1999 年に開始された K2K 実験では、後置検出器として加速器で生成されたニュートリノビームを検出し、さらにはその次期実験である T2K 実験でも同様に後置検出器として用いられる予定である。

スーパーカミオカンデにおいては上に挙げたような様々な研究が行われているが、この章ではこれらの研究対象についてそれぞれ物理的な背景を述べる。さらに、本研究のテーマであるデータ収集エレクトロニクスの開発に関して、それぞれの事象の観測から要請される事項についても述べていく。

## 1.1 ニュートリノ振動

ニュートリノはそもそも、原子核の  $\beta$  崩壊により放出される電子の運動エネルギースペクトルが、二体崩壊から予想されるような線スペクトルにならずに連続スペクトルになることを説明するために、中性の非常に軽い粒子として、1930 年に Pauli により初めてその存在が提唱された。それ以来、様々な実験によりその検出が試みられたが、その相互作用の小ささから検出は困難であった。初めてニュートリノの直接検出がなされたのは、その存在が提唱されてから 20 年あまり経った 1953 年のことであった。検出に成功したのは Reines と Cowan で、彼らは 300 リットルの液体シンチレータを用いて、原子炉からのニュートリノの直接検出に成功した。

ニュートリノの存在はこれにより確認されることとなったが、その質量が完全にゼロであるのか、もしくは、有限な質量を持つのかという問題は、その提唱以来、素粒子物理の一つの問題となってきた。そのニュートリノ質量の測定実験として最も代表的なものは、原子核の $\beta$  崩壊を用いるものである。現在、最も厳しい上限値をつけているのは $^3{

m H}$  の $\beta$  崩壊を用いるもので、その上限値は  $m_{\nu e} < 2.8~{

m eV}~(90\%~{

m C.L.})[1]$  である。しかし、これもニュートリノが有限な質量を持つことを示すには至っていない。

そのような状況の中、1998 年にスーパーカミオカンデにおける大気ニュートリノの観測 [2] によって、ニュートリノ振動の証拠が示されたことにより、ニュートリノに質量があることが強く示唆された。その後、K2K 実験によって加速器で生成されたニュートリノにおいてもニュートリノ振動の存在を確認し、他にも太陽ニュートリノや原子炉ニュートリノの観測を通してもニュートリノ振動は確認され、ニュートリノの質量とともにその存在は現在では確立したものとなっている。

#### 1.1.1 ニュートリノ振動

ここでは、ニュートリノの質量とニュートリノ振動がどのような関係にあるのかについて述べていくことにする。

もし、ニュートリノが有限な質量を持つとすると、フレーバーの固有状態  $|\nu_{\alpha}\rangle(\alpha=e,\mu,\tau)$  とは別に、質量の固有状態  $|\nu_{i}\rangle(i=1,2,3)$  も存在することになる。このとき、フレーバーの固有状態は次のように質量の固有状態の重ね合わせで書くことができる。

$$|\nu_{\alpha}\rangle = \sum_{i} U_{\alpha i} |\nu_{i}\rangle \tag{1.1}$$

ここで、 $U_{lpha i}$  はレプトン混合行列と呼ばれるユニタリ行列であり、次のように表せる

$$U = \begin{pmatrix} c_{12}c_{13} & s_{12}c_{13} & s_{13}e^{-i\delta} \\ -s_{12}c_{23} - c_{12}s_{23}s_{13}e^{i\delta} & c_{12}c_{23} - s_{12}s_{23}s_{13}e^{i\delta} & s_{23}c_{13} \\ s_{12}s_{23} - c_{12}c_{23}s_{13}e^{i\delta} & -c_{12}s_{23} - s_{12}c_{23}s_{13}e^{i\delta} & c_{23}c_{13} \end{pmatrix}$$

(1.2)

ここで、 $s_{ij}=\sin\theta_{ij},c_{ij}=\cos\theta_{ij}$  である。 $\theta_{ij}$  は質量の固有状態 ij の間の混合角、 $\delta$  は複素位相である。

ところで、状態ベクトルの時間変化はシュレーディンガー方程式より次のように書くことができる。

$$|\nu_i(t)\rangle = e^{-i(E_i t - p_i L)} |\nu_i(0)\rangle \tag{1.3}$$

$$E_i = \sqrt{p^2 + m_i^2} \approx p + \frac{m_i^2}{2n} \tag{1.4}$$

ここで、 $m_i$  は質量の固有状態 i の質量、L はニュートリノの伝播した距離であり、 $t \approx L$  としてよい。

以上より、 $\nu_{\alpha}$  として生成したニュートリノが距離 L 伝播したときの状態ベクトルは次のように書くことができる。

$$|\nu_{\alpha}(L)\rangle = \sum_{i} U_{\alpha i}^{*} e^{-i(m_{i}^{2}/2E)L} |\nu_{i}\rangle \tag{1.5}$$

したがって、時刻 t=0 で  $\nu_{lpha}$  として生成し、距離 L 伝搬したときに  $\nu_{eta}$  へと変化している確率は

$$P(\nu_{\alpha} \to \nu_{\beta}) = |\langle \nu_{\beta} | \nu_{\alpha}(L) \rangle|^{2}$$

$$= \delta_{\alpha\beta} - 4 \sum_{i>j} \text{Re} \left[ \sin^{2} \left( 1.27 \Delta m_{ij}^{2}(L/E) \right) \right]$$

$$+2 \sum_{i>j} \text{Im} \left[ \sin^{2} \left( 2.54 \Delta m_{ij}^{2}(L/E) \right) \right]$$

(1.6)

ここで、 $\Delta m_{ij}^2 \equiv m_i^2 - m_j^2 \; [{

m eV}^2]$ 、伝播距離 L は  $[{

m km}]$  で、ニュートリノのエネルギー E は  $[{

m GeV}]$  である。

二世代間のみの混合の場合では一つの混合角  $\theta$  と一つの質量二乗差  $\Delta m^2$  で書くことができ、  $u_{\alpha} \to \nu_{\beta}$  の振動確率は次のようになる。

$$P(\nu_{\alpha} \to \nu_{\beta}) = \sin^2 2\theta \sin^2 \left(\frac{1.27\Delta m^2 L}{E}\right) \tag{1.7}$$

したがって、振動確率の大きさは混合角  $\theta$  で決定され、L/E 依存性は質量二乗差  $\Delta m^2$  で決まることになる。

次節では、これまでに行われたニュートリノ振動実験の中から、特に大気ニュートリノの観測と 太陽ニュートリノの観測について述べていくこととする。

#### 1.1.2 大気ニュートリノ

大気ニュートリノ 大気ニュートリノの起源は、陽子や  $\alpha$  粒子などの一次宇宙線が大気中の原子核と衝突して生成する、  $\pi$  や K などの二次粒子の崩壊によるものである。例えば、 $\pi^\pm$  は次のような過程で崩壊していく。

$$\pi^{+} \to \mu^{+} + \nu_{\mu}$$

$$\to e^{+} + \nu_{e} + \overline{\nu}_{\mu} + \nu_{\mu}$$

$$(1.8)$$

$$\pi^{-} \to \mu^{-} + \overline{\nu}_{\mu}$$

$$\to e^{-} + \overline{\nu}_{e} + \nu_{\mu} + \overline{\nu_{\mu}}$$

(1.9)

したがって、 $\pi^\pm$  の崩壊からはミューオンニュートリノと電子ニュートリノが 2:1 の割合で生成されるので、フラックスの比  $R=(\nu_\mu+\overline{\nu}_\mu)\,/\,(\nu_e+\overline{\nu}_e)$  は 2 になると期待される。ただし、高エネルギーのミューオンは地上まで崩壊せずに届く割合が大きくなるために、数  ${\rm GeV}$  以上の領域では地表での電子ニュートリノのフラックスは小さくなる。したがって、ニュートリノのエネルギーが大きいほど、フラックスの比 R は大きくなる。

一方、式 (1.8)、(1.9) の過程により生成した大気ニュートリノは地球を貫通して全方向から到来することになる。したがって、その飛行距離は到来方向によって異なり、 $15~\rm km$  程度から  $13000~\rm km$  にまで及ぶこととなる。

大気ニュートリノの観測とニュートリノ振動 大気ニュートリノは、もともとカミオカンデや IMB、Soudan2、Fréjus、Nusex などの陽子崩壊探索実験において、主要なバックグラウンドと なることから、精密な測定が行われるようになった。ところが、その測定が進むにつれて、大気ニュートリノにおけるフレーバーの比  $R(\mu/e)$  が期待される値より小さく、約 60~% 程度であることがカミオカンデや IMB から報告されるようになり、このことは「大気ニュートリノ異常」として議論されることとなった。しかしながら、Fréjus や Nusex での観測からのフレーバーの比は期待値と有意な差は見られなかった。このことから、カミオカンデや IMB におけるフレーバーの比の異常は水チェレンコフ検出器の粒子識別能力の問題ではないかとも考えられた。そのため、カミオカンデのプロトタイプとして KEK に建設された 1kt の水チェレンコフ検出器を用いたビームテストが行われ、ミューオンと電子の識別に問題の無いことが確かめられた。

カミオカンデの後継実験であるスーパーカミオカンデでは統計量を大きく伸ばし、1998 年には  $\nu_{\mu}$  の天頂角分布において、地球内部を通過してきた  $\nu_{\mu}$  による上向き事象の数が減少していることを観測した。さらに、その上向き事象の減少は  $\nu_{\mu} \leftrightarrow \nu_{\tau}$  の二世代間の振動で説明できることを示し、これをニュートリノ振動の証拠として発表した [2]。

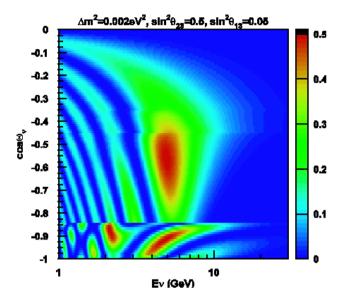

大気ニュートリノ観測における今後の課題 大気ニュートリノ観測における今後の課題の一つは 大気ニュートリノにおいて  $\nu_{\mu} \to \nu_{e}$  の振動モードを観測することである。現在までにはこの振動 モードは大気ニュートリノ観測を始め、加速器による実験でも確認されていないが、最近の計算結 果から、 $\nu_{\mu}$   $\nu_{e}$  の二世代間の混合角  $\theta_{13}$  を 0 でないと仮定したとき、図 1.1 のように数 GeV の狭 い領域で  $\nu_{\mu} \rightarrow \nu_{e}$  の振動確率が大きくなる領域があることが分かっている。この振動モードを観測することができれば、 $\theta_{13}$  が 0 でないことの初めての証拠となる。

図  $1.1 \sin^2 \theta_{13} = 0.05$  を仮定して計算された  $\nu_{\mu} \rightarrow \nu_{e}$  の振動確率

大気ニュートリノ観測からのエレクトロニクスへの要請 大気ニュートリノのような数 TeV にまで及ぶような高エネルギー事象では一つの光電子増倍管で観測される光電子の数は 1000 p.e.\*1 程度にまで及ぶ大きなダイナミックレンジを持つ。したがって、大気ニュートリノ観測では、電荷情報、時間情報の両方が重要になる。まず、反応点の再構成においては主に各光電子増倍管のヒットの時間情報が使われる。(ヒットとは、各チャンネルに入力された信号がディスクリミネータの閾値を越えることである。以下、特にことわりの無い限りヒットとはこの意味で使われる。) したがって、エレクトロニクスへの要請の一つ目としては、光電子増倍管の時間分解能より十分良い時間分解能を持つことが挙げられる。特に、高エネルギー事象では 1000 p.e. にも及ぶような大きな信号が入ることになり、一般的にそうした大きな信号では光電子増倍管の時間分解能も良くなることから、エレクトロニクスとしては光電子増倍管の性能を常に上回っている必要がある。また、エネルギーの再構成は、簡単には全ての光電子増倍管で観測された光電子の総数から計算することでなされるから、電荷の測定を精度良く行う必要と大きな信号に対しても飽和することの無い十分なダイナミックレンジが必要となる。

電荷の測定精度に関してはエネルギーを決定する際の不定性より十分小さくする必要があるだろう。ここで、電荷の精度と言うのは、絶対精度のことではなくて、相対的な測定精度のことである。 というのは、絶対的な電荷の値は一光電子分布から決定されるため、エレクトロニクスでの絶対的

$<sup>^{*1}</sup>$  photo electron の略。光電子増倍管で観測される電荷が光電子何個分に相当するかという意味で、電荷の単位のようにも使われる。

な電荷の測定値は重要ではないからである。重要なのは、相対的な測定精度である。大気ニュートリノにおいてエネルギーを求めるときの不定性は  $\pm 2~\%$  であるから、相対的な測定精度は個体差や温度変化による影響を受けるが、その影響化でも電荷測定の精度として 1~% の精度は必要である。

また、大気ニュートリノのような高エネルギー事象でも 1 p.e. の電荷のデータは多く (リング数の決定や粒子識別に重要となる)、さらに、大きな電荷の測定においてもその基準となるのは 1 p.e. の電荷である。したがって、1 p.e. の電荷の測定精度は非常に重要となる。1 p.e.  $(\sim 2$  pC) レベルの信号に対しても 1 % に近い相対精度で測定できる必要がある。そのためには、エレクトロニクスの電荷分解能は少なくとも 0.1 pC 程度である必要があるだろう。

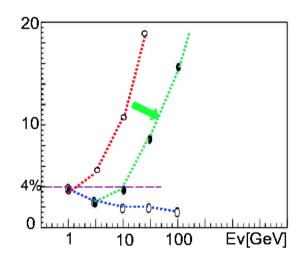

一方、ダイナミックレンジに関しては、エネルギーの高い粒子が多く発生するような事象では一つの光電子増倍管では 1000 p.e. 程度まで観測されることから、1000 p.e. 程度までの電荷を測定できることが求められる。しかし、現在のエレクトロニクスでは約 200 p.e. までの電荷しか測定できない。したがって、高エネルギー事象に対しては現在のダイナミックレンジは十分ではなく、図 1.2 の赤色の線で示されるように、 GeV 以上の領域ではエネルギー分解能が悪くなるという現象が見られている。これを現在の 5 倍の 1000 p.e. にまで拡大した場合の分解能が図 1.2 中の緑色の線である。これにより、10 GeV までのエネルギー分解能を 4 % 以下に抑えることが可能となる。このエネルギー領域は大気ニュートリノ観測における今後の課題のところでも述べたように、 $\nu_{\mu} \rightarrow \nu_{e}$  振動の観測のために重要な領域であり、図 1.1 のような狭いエネルギー領域での振動を見つけるためにはエネルギー分解能が十分良いことが欠かせない。

図 1.2 シミュレーションによって求められたダイナミックレンジとエネルギー分解能との関係。横軸はニュートリノのエネルギー、縦軸はエネルギー分解能である。赤色の線は現在のエレクトロニクスによる分解能、青色の線はどのような電荷に対しても飽和の無い理想的なエレクトロニクスを仮定したときのエネルギー分解能である。緑色の線は電荷測定のダイナミックレンジを現在の 5 倍の 1000 p.e. と仮定したときの分解能である。

さらに、検出器内で止まったミューオンの崩壊に伴う電子の観測も粒子識別とエネルギー較正の二つの意味で非常に重要である。ミューオンの寿命は  $2.2~\mu sec$  であるから、数  $\mu sec$  間隔の連続した信号を取りこぼすこと無く取得できるようなエレクトロニクスが必要である。現在のエレクトロニクスでは二つまでの連続した信号を取得することを考えて構成されているのだが、最初の信号が入力されてから 400~n sec から 900~n sec までの間はデッドタイムとなってしまっている。もし、最初に信号が入力されたと同時にミューオンが検出器内で止まったとすれば、400~n sec から 900~n sec までの間に崩壊する確率は 17~% で、その間に崩壊した電子の信号を同じチャンネルでは取得できない。このデッドタイムの要因の一つはインピーダンスの不整合による信号の反射であり、新しいエレクトロニクスでは高精度なインピーダンスの整合を実現することも求められる。

#### 1.1.3 太陽ニュートリノ

太陽ニュートリノ発生機構 太陽をはじめ、恒星のエネルギー源が何であるかということは古来から大きな謎であった。核融合反応が発見されるまでは、化学反応や重力エネルギーなどのエネルギー源が考えられていたが、現在では太陽の質量とその年齢からまったく説明できないことが明らかになっている。現在では、水素原子核 4 個が核融合反応を起こしてヘリウム原子核となる水素の熱核融合反応が太陽のエネルギー源であると考えられている。この水素の核融合反応には CNOサイクルと p-p チェインの二種類があるが、太陽内部では主に p-p チェインが起こっていると考えられている。この p-p チェインは 3 つの分岐枝を持つが、結果的には次のような反応式で記述できる。

$$4p \to 4 \text{ He} + 2e^+ + 2\nu_e + 26.7 \text{ [MeV]}$$

(1.10)

式 (1.10) から分かるように、太陽内部の核融合反応からは大量のエネルギーとともにニュートリノが放出されている。もし、太陽のエネルギー源が全てこの反応によるものであるとすれば、 $6\times 10^{10}~[{

m cm}^{-2}{

m s}^{-1}]$  のニュートリノフラックスが地球に降り注いでいることになる。

p-p チェインにおいて、ニュートリノが発生する反応は次の 5 つである。

$$p + p \rightarrow {}^{2}\text{H} + e^{+} + \nu_{e} \qquad (0 < E_{\nu} < 0.42 \text{ [MeV]})$$

(1.11)

$$p + e^{-} + p \rightarrow {}^{2}\text{H} + \nu_{e}$$

$(E_{\nu} = 1.44 \text{ [MeV]})$  (1.12)

$$^{7}\text{Be} + e^{-} \rightarrow ^{7}\text{Li} + \nu_{e} \qquad (E_{\nu} = 0.38, 0.86 \text{ [MeV]})$$

(1.13)

$$^{8}\text{B} \to {}^{8}\text{Be}^{*} + e^{+} + \nu_{e} \qquad (0 < E_{\nu} < 14.06 \text{ [MeV]})$$

(1.14)

$$^{3}\text{He} + p \rightarrow ^{4}\text{He} + e^{+} + \nu_{e} \qquad (E\nu < 18.77[\text{MeV}])$$

(1.15)

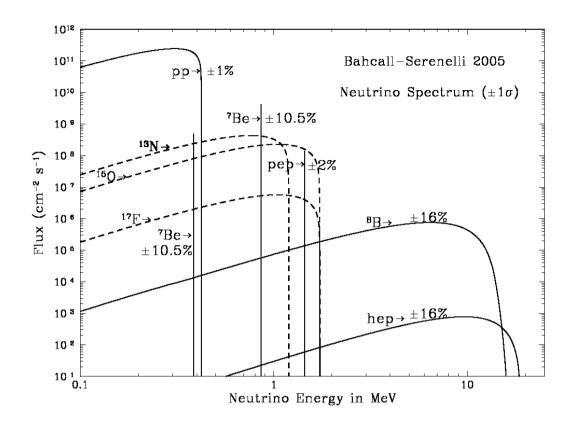

スーパーカミオカンデのエネルギー閾値は数 MeV (時期により違うが、およそ  $4\sim6~MeV$ ) であるから、スーパーカミオカンデにおいて観測可能であるのは、主に式 (1.14) の  $^8B$  の反応により生成されたニュートリノである。(式 (1.15) の反応により生成されたニュートリノはエネルギー閾値としては観測可能であるが、図 1.3 にあるようにフラックスは非常に小さく、スーパーカミオカンデにおいて観測されていると断言することは現段階ではできない。)

太陽ニュートリノ問題 太陽ニュートリノは 1960 年代終わりに Davis らによって初めて観測された [5]。 Davis らは次の反応によって、検出器中の  $^{37}\mathrm{Cl}$  が  $^{37}\mathrm{Ar}$  へと変化する量から太陽ニュー

図 1.3 太陽ニュートリノのエネルギースペクトル [4]

トリノのフラックスを観測した。

$$\nu_e + ^{37} \text{Cl} \to e^- + ^{37} \text{Ar}$$

(1.16)

ところが、この実験で測定された太陽ニュートリノのフラックスは理論値の約 1/3 しか無いことが分かった。その後行われたカミオカンデや GALLEX、SAGE などの太陽ニュートリノの観測においても、やはり、太陽ニュートリノフラックスの測定値は理論値の 1/3 から 1/2 程度しかないことが確かめられた。このことは太陽ニュートリノ問題として天体物理学における難問の一つとして残ることとなった。

この問題の解として、最も有力であったのが物質中でのニュートリノ振動、すなわち、MSW 効果によって、 $\nu_e$  が欠損しているという解である。しかし、カミオカンデやそれまでの実験からは決定的な答えは出せていなかった。

スーパーカミオカンデにおける太陽ニュートリノ観測 スーパーカミオカンデにおける太陽ニュートリノの観測では、水中で以下の反応により弾性散乱された反跳電子を検出する。

$$\nu_x + e \to \nu_x + e \tag{1.17}$$

この反応は全てのニュートリノのフレーバー  $(

u_e,\

u_\mu,\

u_ au)$  に対して中性カレント反応を通して

起こり、さらに、 $\nu_e$  に対しては荷電カレント反応によっても  $e^-$  は生成される。したがって、 $\nu_e$  に対する断面積は  $\nu_\mu$ 、 $\nu_\tau$  に対する断面積に比べて 6 倍ほど大きい。すなわち、スーパーカミオカンデにおける太陽ニュートリノのフラックスは全てのフレーバーを測定していることになるのだが、 $\nu_\mu$ 、 $\nu_\tau$  に関してはその寄与は  $\nu_e$  の 1/6 である。

1996 年 から 2001 年までにスーパーカミオカンデにおいて測定された太陽ニュートリノ事象は 約 22400 事象であり、それから計算された太陽ニュートリノフラックスは  $2.35\pm0.02(\mathrm{stat.})\pm0.08(\mathrm{sys.})\times10^6~[\mathrm{cm}^{-2}\mathrm{s}^{-1}]$  [6] であった。この結果は標準太陽モデルの予測値の約 41~% となる。

一方、重水を用いた SNO 実験では弾性散乱に加えて、次のような荷電カレント反応と中性カレント反応についても観測することができる。

$$\nu_e + d \rightarrow p + p + e^-$$

(荷電カレント反応) (1.18)

$$\nu_x + d \rightarrow p + n + \nu_x$$

(中性カレント反応) (1.19)

荷電カレント反応では  $\nu_e$  のみのフラックスを測定することができる。そして、重水を用いた SNO 実験の最初の結果 [7] により、荷電カレント反応により観測された太陽ニュートリノのフラックスは予測値の約 35~% であった。

この二つの実験によるフラックスの違いは、太陽ニュートリノフラックスの中に、太陽内部の核融合反応からは生成されないはずの  $\nu_\mu$  もしくは  $\nu_\tau$  が含まれていることを意味し、太陽で核融合反応により生成した  $\nu_e$  が  $\nu_\mu$  もしくは  $\nu_\tau$  へと振動していることの証拠となった。

太陽ニュートリノ観測における今後の課題 スーパーカミオカンデにおける太陽ニュートリノ観測の今後の課題の一つとしては、ニュートリノ振動から予測されるエネルギースペクトルの歪みを観測することが挙げられる。現在はその歪みは観測されていないが、その観測を実現するためには、統計量を増やすとともに、さらに低エネルギー領域の観測が求められる。

太陽ニュートリノ観測からのエレクトロニクスへの要請 スーパーカミオカンデにおいて観測される太陽ニュートリノのエネルギーは 10 MeV 程度である。そのような低エネルギー領域では、発生するチェレンコフ光子の数は非常に少ないから、各光電子増倍管で観測される光電子は殆ど 0か 1 である。したがって、事象の再構成は簡単には以下のように行われる。

- 反応点 ← 各ヒットの時間情報から

- エネルギー ← 何個の光電子増倍管でヒットがあったか

よって、太陽ニュートリノのような低エネルギー事象の観測からエレクトロニクスへと要請されることは次のようになる。

- 1.1 p.e. レベルでの時間分解能が光電子増倍管より十分良いこと

- 2. 1 p.e. レベルの信号に対してノイズが十分小さいこと

- 3. 高頻度の信号を高速に処理すること

このなかで、最初の 1. の要請は自明であると思われるから、後の 2 つについて説明する。

エネルギーの再構成では主に何個の光電子増倍管でヒットがあったかで決定されるのだから、エネルギー分解能はヒットの数が多いほど良くなることになる。一方、光電子増倍管の一光電子分布は次章で述べられるように、図 2.4 のようになるから、フロントエンドエレクトロニクスのディスクリミネータの閾値を下げれば下げるほど、一光電子を捕らえる確率は高くなり、ヒットの数も多くなる。このことから、できるだけディスクリミネータの閾値を下げることが求められるのだが、それには、ディスクリミネータの閾値を十分下げてもエレクトロニクス起因の偽のヒットが生じないように、低ノイズであることが求められるのである。例えば、20 インチ光電子増倍管における 1 p.e. の信号の振幅は約 -3 mV であるから、これに対して十分小さな閾値に設定できることが求められる。さらに、エレクトロニクスの低ノイズが実現されたとしても、光電子増倍管からくる暗電流を減らすことはできない。したがって、低ノイズなだけではなく、十分高速に処理できることも求められるのである。

現在のエネルギー閾値より、さらに低エネルギーの観測をしようとして、トリガー発生の閾値を低くした場合 (ここでいう閾値とは各チャンネルのディスクリミネータの閾値とは異なる)、バックグラウンドなどによる事象の頻度は非常に高くなることが予想される。そうなった場合、もはや、(トリガーの生成によらず) 常時全てのヒットをエレクトロニクスでは取得してしまって、その後、多数の計算機でいらないデータを落としていくという方法も選択肢の一つとなり得る。したがって、新しいエレクトロニクスへの具体的な目標としては、(実際に実現するかはともかく)全てのヒットの情報を、エレクトロニクスからオンラインのデータ収集システムの段階では取得できる、という性能にしておくことである。具体的な数字としては、現在の光電子増倍管の暗電流によるヒットの頻度は平均で約3 kHz であるから、ある程度のマージンをとって、全てのチャンネルで常時10 kHz のヒットがあったとしても、オンラインでは全てのヒットを取得し、全てを記録することをデッドタイム無く行うシステムが求められる。

#### 1.2 超新星爆発ニュートリノ

超新星爆発 太陽ニュートリノの発生機構のところで、太陽など恒星のエネルギー源は水素の核融合反応であると述べた。最終的には、核融合反応は止まってしまい、星は重力収縮を起こし、重力エネルギーを解放する。そのときに起こる大爆発が超新星爆発である。

太陽の約8倍以上の大質量の星においては、コアの水素が尽きると、続いて、ヘリウム、炭素などの核融合反応が続き、最終的には鉄のコアができる。鉄は最も安定な原子核であるから、ここで核融合反応は止まることになる。その結果、鉄のコアの収縮が進み、中心の温度は $3 \times 10^9~[{

m K}]$ を超える高温になる。すると、式 (1.20) のような光分解反応が起こることによって鉄がヘリウムと中性子に分解し、さらには続く反応 (1.21) で、陽子が生成される。

$$^{56}\text{Fe} + \gamma \to 13^4\text{He} + 4n - 124.4 \text{ [MeV]}$$

(1.20)

$$^{4}\text{He} \rightarrow 2p + 2n - 28.30 \text{ [MeV]}$$

(1.21)

この陽子は式(1.22)のように電子捕獲反応を起こすことになる。

$$p + e^- \to n + \nu_e \tag{1.22}$$

これにより電子の数が少なくなるので、電子の縮退圧が小さくなり収縮はさらに進むことになる。この過程により、大量のニュートリノが発生するが、密度が  $10^{11}~{

m g~cm^{-3}}$  を超えるような neutrino sphere と呼ばれる高密度の領域ではその高密度の物質に遮られ、ニュートリノでさえ もコアの外へと出ていくことはできないため、この時点では放出されるエネルギーへの寄与は小さい。

重力収縮が進むにつれ、コアの密度は原子核の密度と同程度の高密度  $(3 \times 10^{14} \mathrm{~g~cm^{-3}})$  にまでなる。すると、今度は核力による反発によりコアの収縮は止められる。そこに外側の物質が超音速で自由落下してきて、コアにぶつかり跳ね返され、外側へと衝撃波をつくる。これをバウンスという。この衝撃波が届いた領域では、陽子や中性子が束縛状態から解放され、再び電子捕獲反応が起き、大量の  $\nu_e$  が放出される。これが最初のニュートリノバーストとなる。このバーストは  $10 \mathrm{msec}$  のタイムスケールを持ち、放出されるエネルギーは数  $10^{51}$  erg である。

この最初のバーストの後、衝撃波により高温となった領域では、次のような反応が起き、このと きには全てのフレーバーのニュートリノが生成される。

$$\gamma^* \to e^+ + e^- \to \nu + \overline{\nu} \tag{1.23}$$

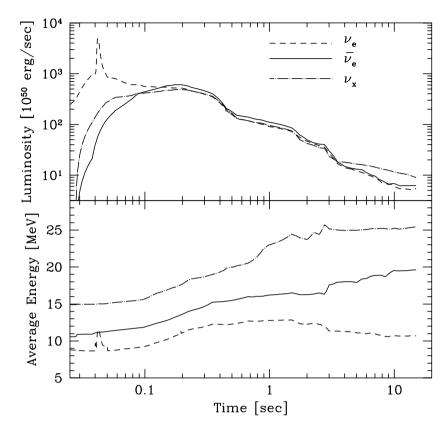

このときに放出されるエネルギーは数  $10^{53}$  erg でおよそ 10 sec にわたって、放出される。 以上の様子を表したのが、図 1.4 である。数 10 msec 後に最初の  $\nu_e$  によるピークがあり、それから約 10 sec かけて全てのフレーバーのニュートリノが放出されている様子が計算されている。

カミオカンデによる 1987A の観測 1987 年 2 月 23 日、地球から  $50~\rm kpc$  離れた大マゼラン星雲に超新星 1987A が現れた。このときのニュートリノバーストによるニュートリノはカミオカンデにおいて  $11~\rm san$  が観測された [9]。この超新星爆発のニュートリノの観測は史上始めてのものであり、さらに IMB においてもカミオカンデが観測した時刻と同時刻に  $8~\rm san$  san  $8~\rm san$  san  $8~\rm san$   $9~\rm san <math>9~\rm san$  san  $9~\rm san$  san  $9~\rm san <math>9~\rm san$  san  $9~\rm san$  san  $9~\rm san$  san  $9~\rm san <math>9~\rm san$  san  $9~\rm san ~\rm san ~\rm$

スーパーカミオカンデにおける超新星爆発の観測 もし、約 10 kpc 離れた銀河中心において超新星爆発が起きた場合、スーパーカミオカンデでは約 10000 もの事象を観測することができると計算されている。したがって、カミオカンデにおける観測ではその統計の少なさからできなかった様々な研究が可能となると考えられる。

例えば、光では遮られて観測ができなかった超新星爆発もニュートリノの観測からその方向を知ることができるということもその一つである。スーパーカミオカンデにおける観測は主に次の荷電カレント反応により生成された反電子を観測することになる。

$$\overline{\nu_e} + p \to n + e^+ \tag{1.24}$$

図 1.4 超新星爆発により放出されるニュートリノの光度とエネルギーの時間変化 [8]

それ以外にも次のような弾性散乱による  $100 \sim 150$  事象が観測されると計算されている。

$$\nu_x + e^- \to \nu_x + e^- \tag{1.25}$$

この反応で散乱される電子は到来してきたニュートリノの到来方向と強い相関をも持つために、 超新星爆発の方向を 4°の精度で測定することができる。

また、上に述べたような超新星爆発のモデルはまだまだ不定性の大きなものであり、十分な検証がなされたとは言えない。したがって、超新星爆発のモデルの検証のためにも、最初の  $10~\mathrm{msec}$  に起こるニュートリノバーストの観測やエネルギースペクトルの観測も欠かすことはできない研究である。

超新星爆発ニュートリノ観測からのエレクトロニクスへの要請 超新星爆発からのニュートリノのエネルギーは約  $10~{

m MeV}$  であるから、エレクトロニクスへの要請としては太陽ニュートリノ観測からの要請と同様な要請がある。

しかし、それに加えて超新星爆発のニュートリノの観測では、短い時間 ( $\sim 10~{

m sec}$ ) に平均して約  $1~{

m kHz}$  もの高頻度の事象 (銀河中心での超新星爆発の場合) が発生するという特徴がある。ニュートリノバーストの時間変化を追うのは非常に重要であるから、 $10~{

m sec}$  にわたる事象を全て正確に取り込む必要がある。したがって、次の二つの意味においてデッドタイムの無いシステムが必要と

なる。

- 1. 高頻度の事象を全て逃さず取得する

- 2. いつ起こるか分からない事象を観測する

このためにはまずはシステム全体の高速化が求められる。また、高速化が難しい場合にはそのボトルネックとなる箇所の直前に予想されるデータを取り込んでおけるバッファを用意する必要がある。

また、 $1~\rm kHz$  のトリガーレートというのは超新星爆発が銀河中心で発生したと仮定してのことである。もし、これがその 1/10 の距離の約  $1~\rm kpc$  で発生したとなると、そのニュートリノのフラックスは  $100~\rm fe$ にもなると考えられる。そうした場合、トリガーレートは  $100~\rm kHz$  にもなると予想される。現在のシステムでは  $100~\rm kHz$  のトリガーレートに対して追いつくことはできないため、 $1~\rm kpc$  といった距離で超新星爆発が起きた場合には全てのデータを逃さず取得することはできないであろう。したがって、システム全体の高速化が求められる。

### 1.3 新エレクトロニクス開発の動機

これまで、スーパーカミオカンデで行われている研究とそれぞれの観測からのエレクトロニクスへの要請について述べてきた。

当然のことながら、現在のエレクトロニクスは既にこういった要請を満たすために構成されていのだが、いくつかの問題点もあることが分かっている。3章でもまた詳しく述べるが、主な問題点としては以下のようなものが挙げられる。

- 12 チャンネルを処理するフロントエンドボード一枚につき、ADC が一つしかない

- アナログスイッチのクロストーク

- AD 変換の処理待ち時間におこる電流漏れ

- アナログ入力部でのインピーダンスの不整合による反射がある

さらには、次のような問題もある。

- フロントエンドボードが 16 ビットのイベント番号のうち、8 ビットしか持っていない

- 消費電力が大きい

- 故障率の高さ (電解コンデンサの液漏れなど)

これらの問題点の克服がまず新エレクトロニクス開発の課題である。

一方では、大気ニュートリノ、太陽ニュートリノのさらなる精密観測やより近傍の超新星爆発も 捕らえられるようにするためには次のような改善が求められることはこれまでに述べた。

- 電荷測定ダイナミックレンジの拡大

- 低ノイズ化

#### ● 処理速度の高速化

- ミューオン崩壊の電子事象に対するバックグラウンドの削減

- トリガー発生閾値を下げてトリガーの頻度が大きくなっても処理できるシステム

- 近傍 ( $\sim 1~{

m kpc}$ ) で起きた超新星爆発による  $100~{

m kHz}$  もの高頻度なトリガーレートを処理できるようにする

さらには、エレクトロニクスの改良によって、高エネルギー領域と低エネルギー領域での観測可能領域を拡げることにより、新しく観測、研究可能となる物理も考えられている。以下では、それらの観測から要請されることについて述べる。

#### 1.3.1 高エネルギー領域の観測可能領域の拡大

高エネルギー宇宙ニュートリノの観測 宇宙物理学における大きな問題の一つに TeV を超えるような高エネルギーのガンマ線の起源の問題があるが、その起源の機構として活動銀河核やガンマ線バーストにおける高エネルギーの陽子同士もしくは陽子と光子の衝突による  $\pi^0$  の生成が考えられている。もし、これらが高エネルギーガンマ線の主な起源であるとすれば、次式のような過程も同様に起こると考えられ、この過程により高エネルギーのニュートリノも生成することが考えられる。

$$p + \gamma \to X + \pi^{\pm}$$

$$\pi^{\pm} \to \nu_{\mu} + \mu^{\pm} \to e^{\pm} + \overline{\nu_e} (\nu_e) + \nu_{\mu} + \overline{\nu_{\mu}}$$

(1.26)

したがって、宇宙起源の高エネルギーのニュートリノは宇宙線起源と密接な関連があると考えられており、いくつかの実験がその観測のために始まりつつある。

この高エネルギーのニュートリノのフラックスはモデルによっては、数 10 TeV 以上のエネルギー領域で大気ニュートリノのフラックスを超えるという計算もある。しかし、何度か述べているように、スーパーカミオカンデにおける観測では、このエネルギー領域は電荷測定のダイナミックレンジの不足により、正しい電荷測定ができなくなるという問題が起きている。この観測のためにも電荷測定のダイナミックレンジの拡大は求められる。

#### 1.3.2 低エネルギー領域の観測可能領域の拡大

超新星残骸ニュートリノの観測 過去に起きた超新星爆発によって放出されたニュートリノは拡散して、現在もニュートリノバックグラウンドとして宇宙空間に存在するはずである。この拡散したニュートリノのことを超新星残骸ニュートリノと呼んでいる。

超新星残骸ニュートリノ検出には、低エネルギー領域での太陽ニュートリノによるバックグラウンド、高エネルギー領域での大気ニュートリノによるバックグラウンドがある。しかし、約 20 ~ 35 MeV にちょうど両方のバックグラウンドが小さくなる領域があるため、観測にはこのエネルギー領域が用いられる。ただし、それでもまだ深刻なバックグラウンドは残っており、

$$\nu_{\mu} + N \to \mu + X \tag{1.27}$$

で生成したミューオンのエネルギーがトリガーにかからないほど低く、かつ、崩壊して電子を放出した場合、観測された情報からは  $\nu_e$  による事象であると区別できないのである。これにより、現在のスーパーカミオカンデによる上限値はこの  $\nu_\mu$  バックグラウンドにより決定されてしまっている。

この  $\nu_{\mu}$  バックグラウンドの区別のためには以下のような方法がある。

- 1. トリガーのかかる数  $\mu sec$  以前の情報から、トリガーにもかからないような  $\mu$  の微小な信号見つける。

- 2. 次のような逆  $\beta$  崩壊によってできた中性子が約 200  $\mu sec$  後に陽子に捕獲されて 2.2 MeV のガンマ線を放出する反応を見つける。

$$\overline{\nu_e} + p \to n + e^+ \tag{1.28}$$

$$n + p \to d + \gamma \tag{1.29}$$

現在のエレクトロニクスはこれらのどちらの実現も難しい。というのは、現在のエレクトロニクスでは、トリガーのかかる前の数  $\mu sec$  の情報は取得できず、さらに、時間測定のダイナミックレンジは  $200~\mu sec$  より遥かに小さいからである。このため、新しいエレクトロニクスでは、トリガーのかかる前の情報を取得することとがまず求められ、さらには、約  $200~\mu sec$  の間強制的にトリガーをかけ続けるといったトリガーの改良も考えられる。

原子炉ニュートリノの観測 原子炉からは  $^{235}$ U や  $^{239}$ Pu が核分裂することに伴って放出される  $\overline{\nu_e}$  が放出される。これを検出するためには超新星残骸ニュートリノの観測と同じように式 (1.28)、(1.29) の信号を見つけなければならない。

さらに、原子炉ニュートリノの測定のためには現在より観測エネルギー閾値を大きく下げる必要がある。そして、エネルギー閾値を下げることで、トリガー発生の頻度は高くなることが予想される。例えば、事象の発生頻度が  $100~\mathrm{kHz}$  にもなってしまった場合について考えてみる。そうした場合、事象間の時間差は平均して  $10~\mu\mathrm{sec}$  となり、時間測定のダイナミックレンジを拡げるという要請と同時に実現してしまうと、殆ど常時データを取得し続けるという状態と変わらなくなってしまう。したがって、太陽ニュートリノ観測エネルギー閾値の低下の為の要請と同じく、トリガー生成に関わらず常に全てのヒットを取得できるようにすることが必要となってくる。

### 1.3.3 新エレクトロニクスへの要請のまとめ

様々な要請をばらばらに述べたので、最後にまとめて表にした。表は新しいエレクトロニクスへ の改善点とこれまでのエレクトロニクスにも要請されていた点の二つに分けた。

これらを実現するためのシステムの設計に関しては4章で述べることになる。

表 1.1 エレクトロニクスへの要請

| <br>電荷測定 (相対) 精度 | 1 % 以下                               |

|------------------|--------------------------------------|

| 電荷分解能            | $0.1~\mathrm{pC}$                    |

| 時間測定精度           | 光電子増倍管より十分小さいこと                      |

| デッドタイムの無い読み出し    | 超新星爆発とミューオン崩壊の信号の取得のため               |

| 低ノイズであること        | 現状で $-1~\mathrm{mV}$ のディスクリミネータ閾値が可能 |

表 1.2 新エレクトロニクスの新たな改善目標

| 改善項目              | 改善目標                                           |

|-------------------|------------------------------------------------|

| 電荷測定ダイナミックレンジ     | 2500 pC (~ 1000 p.e.) まで                       |

| 時間測定のダイナミックレンジ    | トリガー前後の数 $\mu { m sec}$ の事象の取得                 |

| 低ノイズ化             | ディスクリミネータ閾値を $-0.5~\mathrm{mV}$ まで下げる          |

| 低消費電力化            | 1 W/ch 以下                                      |

| 高精度のインピーダンス整合     | 反射係数 $0.1~\%$ 以下                               |

| トリガーの改良           | 中性子による約 $200~\mu{ m sec}$ 遅延した信号の取得            |

| AD 変換、データ転送などの高速化 | ミューオン崩壊電子事象に対するデッドタイムの削減                       |

|                   | 常時 $10~\mathrm{kHz/ch}$ の暗電流によるヒットの処理          |

|                   | 約 $10~{ m sec}$ 間の $100~{ m kHz}$ の超新星爆発の信号の処理 |

# 2 スーパーカミオカンデ

#### 2.1 測定原理

物質中で荷電粒子が光の位相速度よりも速い速度で走ると、チェレンコフ光と呼ばれる光が放射 される。スーパーカミオカンデではこの光を検出することにより様々な事象を観測する。

物質中での光の速度は屈折率をnとすればc/nであるから、荷電粒子の速度をvとすれば、 チェレンコフ光を放射するためには次の条件を満たす必要がある。

$$v > \frac{c}{n} \tag{2.1}$$

水の屈折率は 1.33 であるから各粒子のチェレンコフ光を放出できる最小のエネルギーは表 2.1 のようになる。

表 2.1 チェレンコフ光を放出する最小の (全) エネルギー

|             | エネルギー閾値 [MeV] |

|-------------|---------------|

| $e^{\pm}$   | 0.77          |

| $\mu^{\pm}$ | 157           |

| $\pi^{\pm}$ | 208           |

チェレンコフ光は一種の衝撃波と考えられるから、その放射される方向は荷電粒子の進む方向との角度を $\theta$ とすれば、次の条件を満たすような円錐状に放出される。

$$\cos \theta = \frac{1}{n\beta} \tag{2.2}$$

ここで、 $\beta = v/c$  である。

また、単位長さ当たり、単位波長当たりに放出されるチェレンコフ光子の数は次の式で表される。

$$\frac{dN}{d\lambda dx} = \frac{2\pi\alpha z^2}{\lambda^2} \left( 1 - \frac{1}{n(\lambda)^2 \beta^2} \right) \tag{2.3}$$

ここで、ze は粒子の電荷量である。

これより、その速度が光速に近い  $(\beta \simeq 1)$  荷電粒子が水中を走る場合には放出角度は約 42 ° となり、一般的な光電子増倍管が感度を持つ領域である  $300~\rm nm \sim 600~\rm nm$  の波長領域では  $1~\rm cm$  あたり  $340~\rm dl$  の光子を放出する。

放射されたチェレンコフ光はタンク壁面に取り付けられた光電子増倍管によってほぼ円形の分布で検出される。それぞれの光電子増倍管の位置や時間、電荷の情報から粒子のエネルギー、種類、発生点やその進行方向などの情報をリアルタイムで得ることができる。

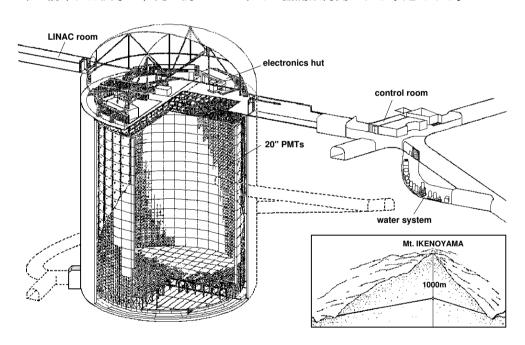

## 2.2 検出器

スーパーカミオカンデで用いられる水チェレンコフ検出器は高さ  $41~\mathrm{m}$ 、直径  $39~\mathrm{m}$  のステンレスでできた円形筒状のタンクの中に、総重量にして約  $50000~\mathrm{h}$  との純水を満たしたものである。その全体図を図  $2.1~\mathrm{km}$  に示す。タンク内は光学的に分けられた内水槽と外水槽がある。内水槽の純水の総重量は約  $32000~\mathrm{h}$  とである。内水槽の壁面には光の反射を抑えるためのブラックシートが張られ、 $11146~\mathrm{km}$  なの  $20~\mathrm{km}$  インチ光電子増倍管が取り付けられ、内水槽壁面に占める光電面の面積は約  $40~\mathrm{km}$  である。また、外水槽はタンクの外の岩盤から放射される  $\gamma$  線や中性子を遮断する役目と、宇宙線ミューオンなどの検出器外部から飛来する荷電粒子のバックグラウンドを識別するという役目がある。そのため、外水槽壁面には光の収集効率を上げるために白いタイベックシートが張られ、  $1885~\mathrm{km}$  8 インチ光電子増倍管が外向きに取り付けられている。

ただし、2001 年に起こった光電子増倍管の破損事故のため、2002 年から 2005 年までの観測は 内水槽の光電子増倍管の数を約 5200 本にして行われた。2005 年後半に開始された完全再建作業 は 2006 年の前半には終了し、元の約 13000 本での観測が再開される予定である。

図 2.1 スーパーカミオカンデ検出器の全体図

#### 2.3 光電子増倍管

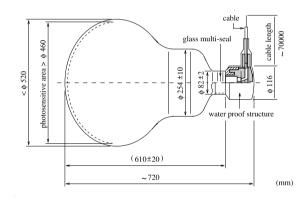

スーパーカミオカンデの内水槽で用いられている直径 20 インチ (50cm) の光電子増倍管は、もともとカミオカンデのために開発された光電子増倍管に改良を加えたものである。その改良により、時間分解能や集光効率などが高められた。全体図を図 2.2 に示す。また、その詳細は [12] に述べられている。

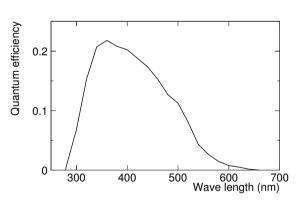

光電面はバイアルカリ (Sb-K-Cs) でできている。その量子効率は図 2.3 に示したように、有感領域は  $280~\rm nm\sim660~\rm nm$  で、 $390~\rm nm$  の波長の光に対して量子効率は最大の 22~% となる。また、印加されている電圧は  $1700~\rm V$  から  $2000~\rm V$  であり、ゲインはおよそ  $10^7$  になる。これより、一つの光電子は約  $2~\rm pC$  まで増幅されることになる。このときの信号の振幅は約  $-3~\rm mV$  になる ( $50~\rm O$  で終端したとき)。

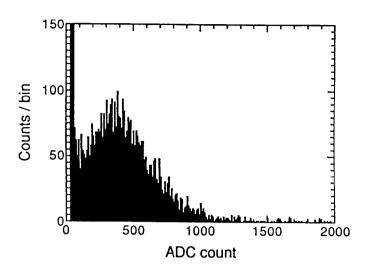

また、20 インチ光電子増倍管の一光電子分布を図 2.4 に示す。一光電子のピークがはっきりと見えていることが分かる。現在、各フロントエンドエレクトロニクスが信号を認識する閾値は、この分布のちょうど「谷」にあたる 1/4 p.e.(= -1 mV) と設定されている。また、1/4 p.e. の閾値にかかる暗電流によるヒットの頻度は平均して約 3 kHz である。

図 2.2 20 インチ光電子増倍管の全体図

図 2.3 20 インチ光電子増倍管の量子効率

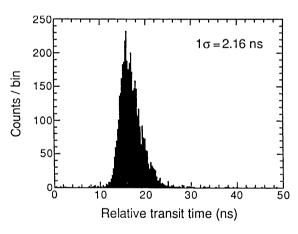

時間分解能 このような大口径の光電子増倍管では、光子が光電面のどこに当たるかによって光電子がダイノードに到達するまでの時間差などが生じてしまう。この時間差を少なくするために第一ダイノードの面積を大きくするなどの改良が行われ、その結果、図 2.5 に見られるように時間分解能 (Transit Time Spread) は 2.2 nsec (1 p.e. の信号において) となった。個体差を考慮しても約 3 nsec の分解能 $^{*2}$ は達せられており、これはカミオカンデに用いられていたものより、約 1.5 倍の改善となった。

$<sup>^{*2}</sup>$  ただし、この測定には光子が光電面のどこに当たるかによって生じる時間差  $(\sim 1 \; \mathrm{nsec})$  も含まれている。

図 2.4 20 インチ光電子増倍管の一光電子分布 [12]。0 付近のピークは暗電流によるものである。

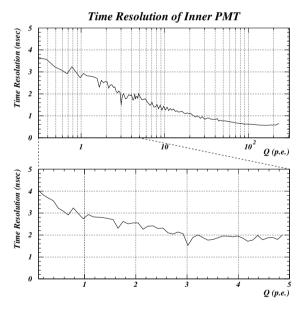

また、信号の大きさと光電子増倍管の時間分解能の関係を図 2.6 に示す。この図から分かるように、光電子増倍管の時間分解能は信号が大きくなるほど向上し、100 p.e. の大きさの信号では 0.6 nsec の時間分解能となる。エレクトロニクスとしてはこの時間分解能を十分上回るものでなくてはいけない。

図 2.5 光電子が発生してから信号が出てくるまでの到達時間の拡がり (Transit Time Spread) [12]。この時間の拡がりが光電子増倍管の時間分解能に相当する。

図 2.6 信号の大きさと 20 インチ 光電子増倍管の時間分解能の関係

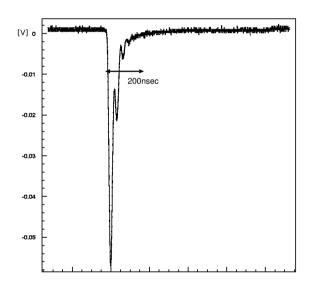

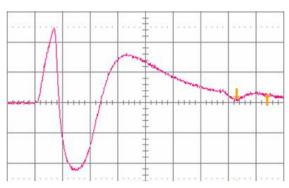

信号の時間特性 光電子増倍管からの信号は全て  $70~\mathrm{m}$  の同軸ケーブルを通って、フロントエンドエレクトロニクスまで到達することになる。同軸ケーブルといえども  $70~\mathrm{m}$  もの距離を伝送させると減衰は無視できなくなってくるので、減衰に対する考慮も必要である。実際の  $70~\mathrm{m}$  の同軸

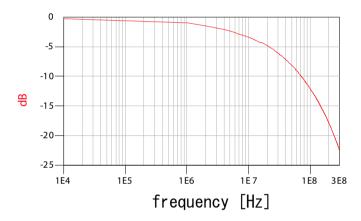

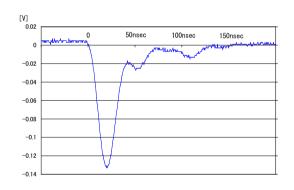

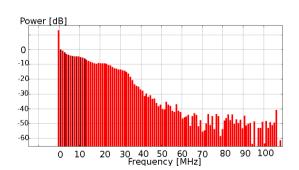

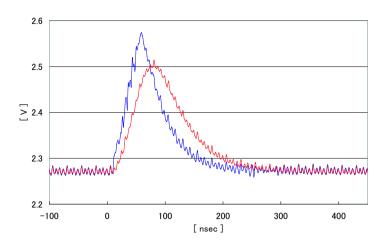

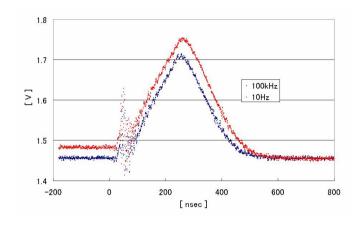

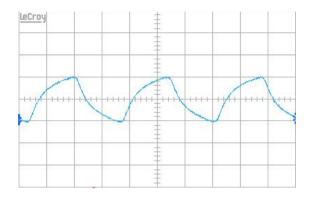

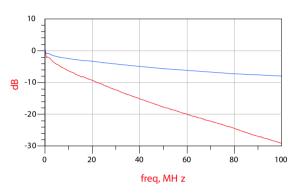

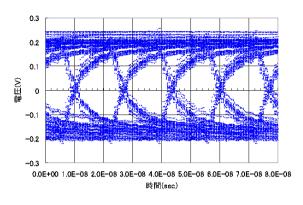

ケーブル (RG-58) の減衰の周波数特性を図 2.7 に示す。この図から分かるように周波数の高い成分ほど表皮効果などによって 70~m の同軸ケーブルを伝送する途中に減衰してしまう割合が高くなってしまう。その結果として、フロントエンドで観測される光電子増倍管の信号の波形は本来の光電子増倍管の信号の波形から (立上り時間の速い成分が削ぎ落とされて) なまった波形が観測される。実際に観測される信号の立ち上がり時間と立ち下がり時間は図 2.8 のように約 20~nsec である。この波形を FFT(高速フーリエ変換) によって周波数解析した結果が図 2.9 である。この図から電力の殆どの成分はおよそ 30~MHz までに存在していることが分かる。

したがって、フロントエンドのアナログ入力部にはおよそ  $100~\mathrm{MHz}$  の周波数帯域があればよいということが分かるまた、時間分解能などの測定にあたってはこのことを考慮し、できるだけ実際の信号の立ち上がり時間などを再現して測定する必要がある。

図 2.7 70 m の同軸ケーブルの損失の周波数特性。横軸は周波数 [Hz]、縦軸は損失 [dB]。 300 MHz 以上の成分では 1/10~(=-20~dB) 以下になってしまうことが分かる。

図 2.8  $70~\mathrm{m}$  の同軸ケーブルを伝送した後の  $20~\mathrm{t}$  インチ光電子増倍管の波形の例。 $(1~\mathrm{GHz}$  の帯域を持つデジタルオシロスコープで取得した)

図 2.9 図 2.8 の波形の FFT による周波数解析結果

## 2.4 オンラインデータ収集系

データ収集系に関しては次章でまた詳しく述べることになるので、ここでは、ごく簡単な流れを述べるにとどめる。

水槽の上には、セントラルハットと 4 つのエレクトロニクスハットと呼ばれる各種のエレクトロニクスが入った小屋がある。約 13000 本の光電子増倍管からの信号はまず、 4 つのエレクトロニクスハットに送られ、その中で  $AD^{*3}$  変換される。その後、ハットにつき 2 つあるオンライン計算機で処理され、中央のセントラルハットのホストのオンライン計算機へと送られる。

セントラルハットでは、ホストのオンライン計算機が各ハットから集められた光電子増倍管の信号のデータを並べ替えるなどして事象を再構成し、その後、それらの情報はオフライン計算機へと送られる。さらに、セントラルハットにはトリガー生成のためのロジックがあり、各ハットの情報からトリガーの生成の判断を下すこともここで行われる。

#### 2.5 キャリブレーション

スーパーカミオカンデで行われるキャリブレーションは多岐にわたり、主なものを挙げると以下 のようなものがある。

- 水の透過率の測定

- 光電子増倍管の相対利得キャリブレーション

- 相対時間キャリブレーション

- エネルギーキャリブレーション

- LINAC によるキャリブレーション

- <sup>16</sup>N の崩壊を用いたキャリブレーション

- ミューオン崩壊電子によるキャリブレーション

- 検出器内で止まったミューオンによるキャリブレーション

他にも、フロントエンドエレクトロニクスである ATM のキャリブレーションなどがある。

ここでは全てのキャリブレーションについて述べることはせず、エレクトロニクスとの関連から、相対時間のキャリブレーションについてだけについて述べることとする。

相対時間キャリブレーション この相対時間のキャリブレーションでは、同軸ケーブルの長さの個体差についての補正を行うだけでなく、信号の大きさによる依存性の補正も行うことを目的としている。信号の大きさによる依存性とは、信号が大きいほどディスクリミネータの閾値を越えるまでの時間が早くなるという、タイムウォークと呼ばれる効果のことである。

このキャリブレーションには窒素レーザーが使われる。このレーザーから発せられた光は二つに

$<sup>^{*3}</sup>$  Analog to Digital の略。

分けられ、一方は光ファイバーを通してタンク内の拡散ボールに行き、もう一方は光の強度のモニターのために使われる。拡散ボールは  ${

m MgO}$  の粉末を含んだアクリルでできており、光は  ${

m MgO}$  の粉末によって拡散されて放射されることになる。

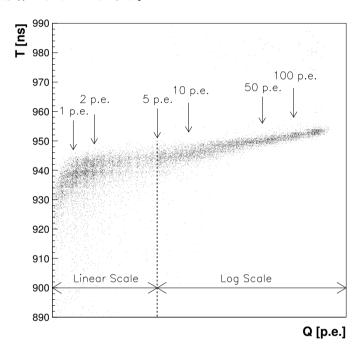

測定はいくつかの光の強度で行われ、その測定結果が図 2.10 である。この図を見ると、約 1 p.e. と約 100 p.e. での時間差は 10 nsec にも及ぶことが分かり、精度の良い時間測定には欠かせない補正であることが分かる。この図のような時間 (T) と電荷 (Q) との関係は TQ-map と呼ばれており、この対応関係は全ての光電子増倍管、チャンネルで異なるため、全てのチャンネルにおいてそれぞれの TQ-map が作られることになる。

図 2.10 TQ-map。横軸は光量、縦軸はヒットの発生時間を表す。この値が大きいほど、ヒットの発生は早いということを示している。

# 3 現行のデータ収集エレクトロニクス

1 章で述べたような多様な事象に対応するためにスーパーカミオカンデにおけるエレクトロニクスには多くの要請が課されている。

この章では、様々な要請を満たすために現在のエレクトロニクスがどのように構成されているかについて述べる。さらに、現在のエレクトロニクスが抱えるいくつかの問題点についてもこの章で述べていくこととする。また、現在のデータ収集システムに関しては [15] [16] [17] [18] [19] にその詳細が述べられている。

## 3.1 データ収集システムの概要

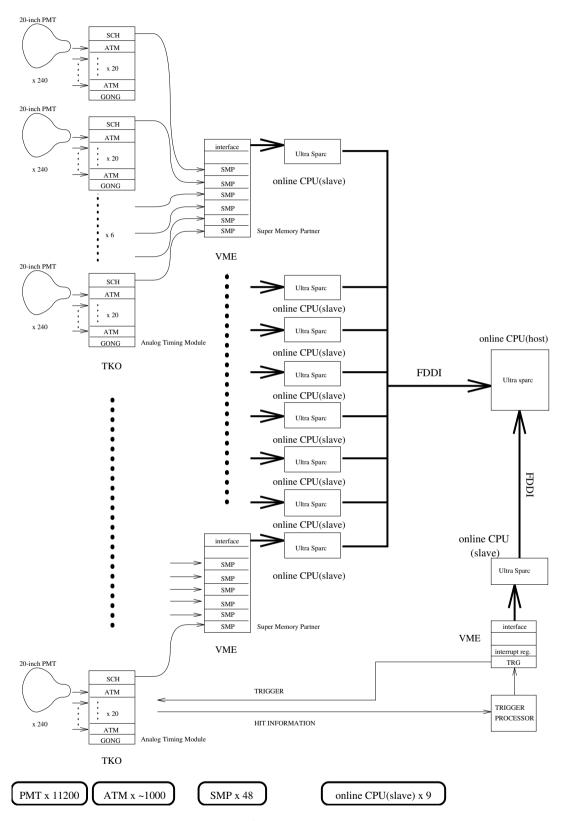

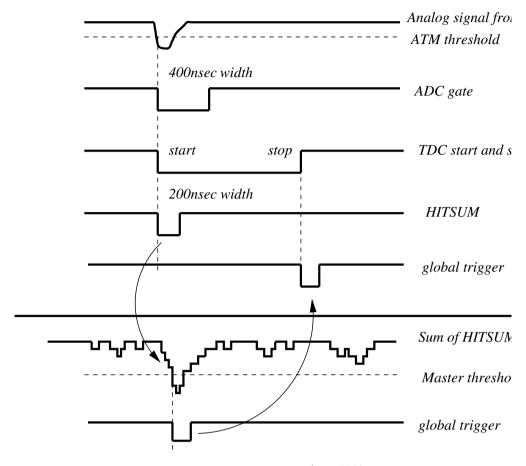

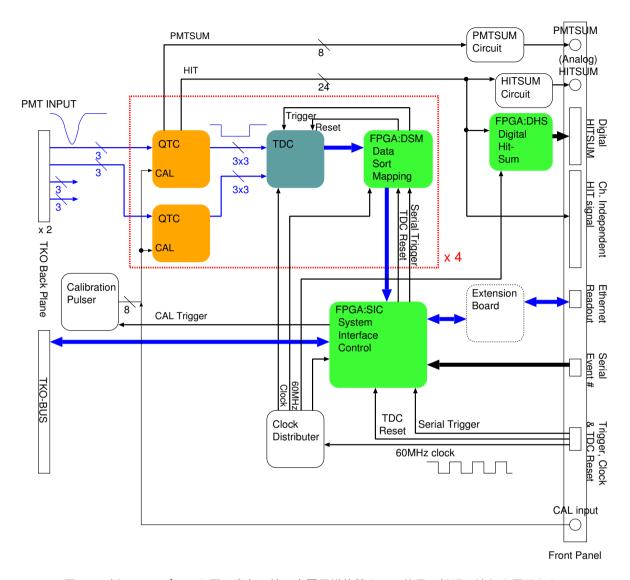

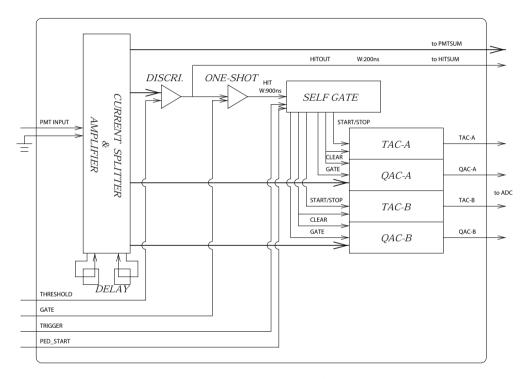

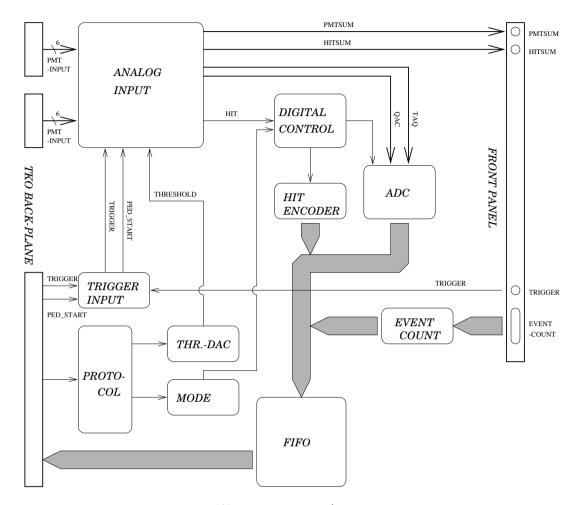

現在のデータ収集システムの全体図を図 3.1 に示す。各光電子増倍管からの信号はまず ATM (Analog Timing Module) と呼ばれるモジュールへと入力される。ATM は 1 章で述べられたような要請を満たすように、スーパーカミオカンデ実験のために開発された TKO\*4 規格のフロントエンドモジュールである。ATM の各チャンネルは光電子増倍管から信号が入力されるとその信号の大きさと到達時間の情報をともに電荷として保持する。この時点では未だその信号が取得すべきものか判断できないために AD 変換までは行わない。ATM は信号入力のあったチャンネルの数に比例した振幅の HITSUM 信号を出す。すべての ATM からの HITSUM 信号は一ヶ所に集められ、それらの振幅は加算される。全ての ATM からの HITSUM の和がある閾値を超えたところで、トリガー生成部はグローバルなトリガーを生成し、その信号は TRG というモジュールを介して全ての ATM へと分配される。グローバルなトリガーを受け取った ATM はそれまで保持していた電荷を ADC により信号の電荷情報と時間情報を同時に AD 変換する。さらに、各 ATM からは PMTSUM 信号としてその ATM へと入力されている信号のアナログ和も出力されており、その出力は Flash ADC へと入力され波形の情報も取得されている。

ATM で AD 変換された信号の情報は、SCH\*5 を介して SMP (Super Memory Partner) と呼ばれるメモリーモジュールへと転送され、一旦格納される。格納されたデータは VME バスを通じてオンライン計算機へと転送され、さらにセントラルハットのオンラインホスト計算機へと集められる。

以上がデータ収集システムの一連の流れである。次節からは、各部の詳細について説明する。

<sup>\*4</sup> Tristan KEK Online の略。Tristan 実験のために KEK の回路室で開発された規格。

<sup>\*&</sup>lt;sup>5</sup> Super Control Head の略。SMP から送られるコマンドに基づいて TKO モジュールを制御し、TKO と SMP 間のデータの送受信を司る。

図 3.1 現在のデータ収集システムの全体図

## 3.2 時間電荷測定モジュール (ATM)

現在の ATM の仕組みの詳細について述べるのは本論文の主旨とはずれるので、ここでは簡単にその特性を述べるにとどめる。ただし、詳細な仕組みを知っておくことは、現在の ATM の問題点の理解の助けになると思われる。そこで、 付録 A にて、現在の ATM に信号が入力されてからの処理の流れを述べておいたので、適宜参照して頂きたい。

#### 3.2.1 現在の ATM の特性のまとめ

ATM の主な特性については表 3.1 にまとめた通りである。

現在の ATM の特徴としては一つの ADC で 12 チャンネルの信号の処理を行うということがある。信号の到来時間と電荷量はそれぞれ TAC と QAC と呼ばれる回路により、電荷に変換されてから ADC により AD 変換されることになる。また、その ADC は 12 ビット分解能であるから、 $0.2~{\rm pC/Count}$  の分解能を求めるとダイナミックレンジは必然的に約  $400\sim600~{\rm pC}$  しかないことになる。

さらに、TAC と QAC は 1 チャンネルにつき、2 つずつあり、連続する信号を取得できるようになっている。ただし、最初の信号が入力されてから 400 nsec  $\sim 900$  nsec の間はデッドタイムとなっている。

また、電荷線型性と時間線型性については直線ではフィットしては十分な精度が得られないため、数 pC(nsec) 毎にとったデータを直線で補間した値が用いられている。

表 3.1 現在の ATM の仕様と特性

| チャンネル数        | 12 ch/board                                            |

|---------------|--------------------------------------------------------|

| 1 ヒットの処理時間    | 約 $5.5 \mu sec$                                        |

| 電荷測定ダイナミックレンジ | 約 400 ~ 600 pC (12 ビット)                                |

| 時間測定ダイナミックレンジ | 約 1300 nsec (12 ビット)                                   |

| 電荷分解能         | $0.2~\mathrm{pC/Count}$                                |

| 電荷測定精度        | $0.2~\mathrm{pC}~\mathrm{(RMS)}$                       |

| 時間分解能         | $0.3 \sim 0.4 \; \mathrm{nsec/Count}$                  |

| 時間測定精度        | $0.4 \operatorname{nsec} (RMS)$                        |

| 温度依存性 (QAC)   | $3~\mathrm{Count/}~\leftrightarrow 0.6~\mathrm{pC/}$   |

| 温度依存性 (TAC)   | $2~\mathrm{Count}/ \leftrightarrow 0.8~\mathrm{nsec}/$ |

| イベント番号        | 8 ビット                                                  |

| 1 ヒットあたりのデータ量 | 6 Byte                                                 |

| FIFO (メモリ)    | 2 kByte ( $\sim 340$ ヒット)                              |

|               |                                                        |

#### 3.3 SMP

SMP とは TKO システムを SCH を通じて制御するモジュールである。このモジュールもデッドタイムの無い読み出しを実現するためにスーパーカミオカンデ実験のために開発された VME 規格のモジュールである。ATM から SMP へのデータ転送は スパースデータスキャンと呼ばれる転送方式であり、その転送レートは実勢で  $\sim 2~{\rm MByte/sec}$  である。スパースデータスキャンではまず  ${\rm GONG^{*6}}$  から  $16~{\rm U}$  ットのイベント番号を読み出し、次に各 ATM のヒットのデータを読み出していく。また、このスキャン中にも ATM は光電子増倍管からの信号を処理することができる。

さらに、SMP は二つのバッファを持ち、一方のバッファがオンライン計算機の方を向き、データが読み出されているときでも、もう一方のバッファでは TKO 側を向き、スパースデータスキャンによりデータを格納することができる。これによって、 $ATM \to SMP$  間の転送はデッドタイム無く行えることになる。

#### 3.4 トリガーシステム

以上では、ATM と SMP を中心として現在のフロントエンドとリアエンドのデータ収集システムの概要を述べてきた。ここでは、トリガーがどのように生成され、また、どのように分配されているかを述べる。

#### 3.4.1 HITSUM

現在のスーパーカミオカンデのトリガー生成は基本的に HITSUM で決定される。HITSUM とは 1 ヒットごとに出力される幅 200 nsec の振幅 -15 mV の HIT 信号の全てのチャンネルの和をとったものである。この HITSUM の信号レベルがある閾値を越えたときにグローバルなトリガーが生成される。

ところで、HIT 信号が 200 nsec である理由は次のとおりである。一つの事象の時間的な拡がりが最大となるのは荷電粒子がタンクの端から端へと斜めに通り抜ける場合であり、チェレンコフ光が斜めに走るのにかかる時間は約 200 nsec である。したがって、HIT 信号を 200 nsec に設定しておけば、どんなに時間的な拡がりを持った事象でも、一つの事象で生成された殆どの HIT 信号はどこかで重なることになるのである。HITSUM とトリガーの関係を図 3.2 に示した。

さて、スーパーカミオカンデにおけるトリガーの種類は主に HE (High Energy)、LE (Low Energy)、SLE (Super Low Energy) の三種類がある。これらの違いは HITSUM の閾値の違いである。HE、LE、SLE の順に閾値は低くなり、それとともにトリガーレートも高くなっていく。

SLE トリガーはこの中でも少し特殊なトリガーで、一種のインテリジェントトリガーである。

$<sup>^{*6}</sup>$  GO NoGo の略。TKO のバスラインを制御するモジュール。スーパーカミオカンデで用いる GONG はさらに ATM の機能を補完する役目も持つ。その一つが 16 ビットのイベント番号を持つことである。

図 3.2 HITSUM とトリガーの関係

ただし、フロントエンドエレクトロニクスとしては本質的には他のトリガーと変わりは無く、トリガーが発せられたら ATM は信号の電荷、時間情報を AD 変換し、SMP へと転送するところまでは同じである。ただし、このときトリガー閾値は非常に低く設定されるので、岩盤からのガンマ線や光電子増倍管自体からの放射、水に含まれるラドンなどからのバックグラウンドによる事象のレートが高くなる。そのために、そのまま全てのデータを残しておいてはデータ量が膨大になってしまう。そこで、このトリガーで取得されたデータはリアルタイムで解析され、フィルターにかけられる。このフィルタリングでは各ヒットの時間情報から反応点を再構成し、反応点が有効体積の外であった場合にはその事象を捨てている。現在では、このリアルタイムの処理に 12 台の計算機を用い、約 1 kHz のトリガーレートに対しても処理できるようになっている。

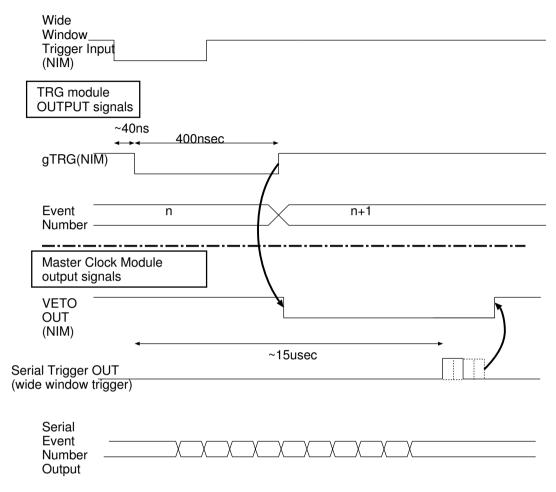

#### 3.4.2 TRG

HITSUM がある閾値を越えて生成された HE、LE、SLE などのトリガーはまず TRG と呼ばれる VME 規格のモジュールに送られる。

TRG はトリガーが入力されると、約 30 nsec 後にグローバルなトリガー信号を発生し、その信号は GONG を介して全ての ATM へと分配される。また、TRG 内では 16 ビットのイベントカウンタを持ち、トリガーの入力によってそのカウンタはインクリメントされる。このイベント番号も GONG を介して全ての ATM へと分配される。ただし、ATM は 8 ビットのイベント番号しか持つことができないので、スパースデータスキャン時に GONG から 16 ビットのイベント番号が読み出されることになる。

さらに TRG のもう一つの大きな機能はトリガーの種類と入力された時間を記録しておくことである。記録されるトリガーの種類に関しては、最初に入力されるトリガーだけではなく、それから約 280 nsec の間に入力されたトリガーの種類も記録される。一方、トリガーの入力時間については、TRG の内部の 50 MHz のクロックでカウントされるカウンタが用意されており、これにより、20 nsec の分解能でイベント間の時間差を知ることができる。このカウンタは 48 ビットのカウンタであるから、カウンタが一回りするまでに約 150 時間かかることになり、データ収集の一つの区切りである「ラン」の最大の時間 24 時間でも同じカウント値は存在しないことになる。

## 3.5 現在の ATM の問題点

1 章でも挙げたように、現在の ATM はいくつかの問題点を抱えている。以下ではそれらの詳細について述べていくことにする。

インピーダンスマッチング 光電子増倍管からの信号が伝えられる同軸ケーブルのインピーダンスは  $50~\Omega$  であるから、ATM への入力インピーダンスも  $50~\Omega$  で終端されていなくてはならない。もし、精度良くインピーダンス整合がなされていない場合には ATM へと入力された信号の一部が反射して光電子増倍管側に流れていくことになる。一方、光電子増倍管側の入力インピーダンスは  $10~\mathrm{k}\Omega$  であるので、光電子増倍管へと入力された信号はほぼ 100~% 反射されてしまい、再びATM へと入力されてしまう。同軸ケーブルの長さは  $70~\mathrm{m}$  であり、同軸ケーブル内での信号の伝播速度は約  $0.2~\mathrm{m}/\mathrm{nsec}$  であるから、反射された信号が再び ATM へと入力されるまでにかかる時間は  $70/0.2 \times 2 = 700~\mathrm{[nsec]}$  となる。

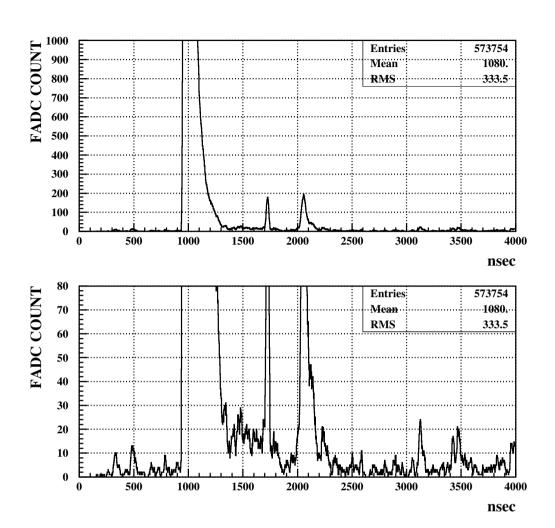

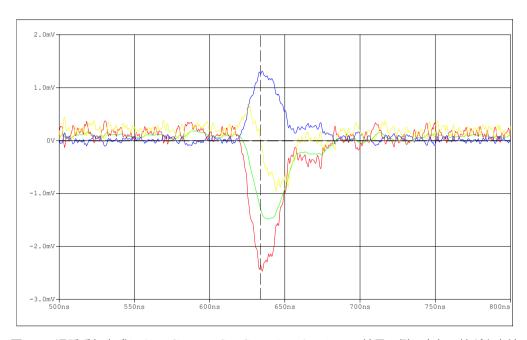

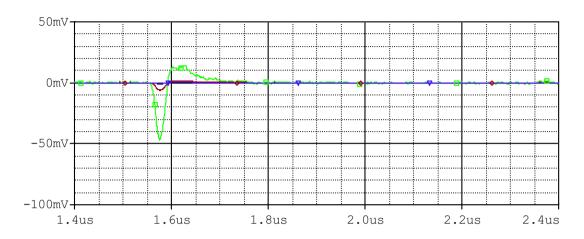

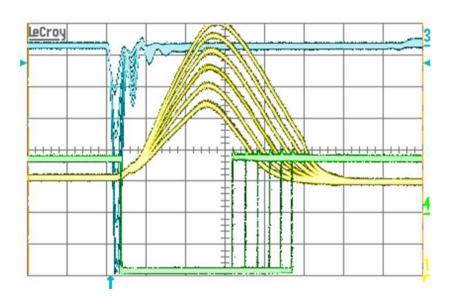

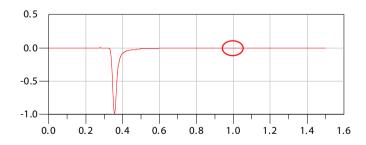

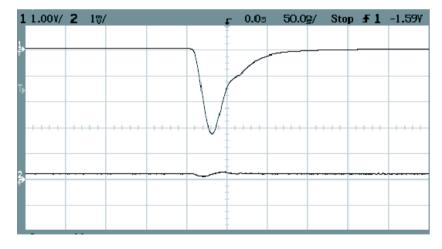

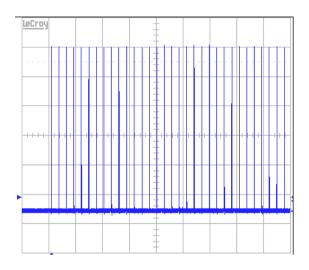

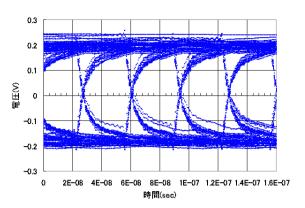

こういった現象が生じるので、インピーダンス整合は精度良くなされているべきであるのだが、 実は現在の ATM は大きな信号が入力されると約 700 nsec 後に約 3 % の振幅の反射波形が観測 されることが分かっている。例として Flash ADC で取得した波形を図 3.3 に示した。

この反射が起こるのはおそらく入力部トランジスタのインピーダンスの周波数特性が考慮されていなかったためで、速い周波数成分を含む信号に対しては、入力インピーダンスが $50~\Omega$ ではなくなってしまうためであると考えられている。大きな信号に対してはこの反射波形もディスクリ

図 3.3 Flash ADC で取得した反射波形。下図は上図の拡大図。1000 nsec 付近の大きな信号がミューオンによる信号であり、その約 700 nsec 後にきている小さな信号が反射による波形である。さらに、2000 nsec 付近の信号はミューオンの崩壊による電子の信号であると考えられる。

ミネータの閾値に十分かかりうるから、この反射波形は偽の事象をつくってしまうことになる。図 3.3 は全てのチャンネルの波形のアナログ和であるからなおさらではあるが、図 3.3 を見た限りでは、ミューオン崩壊の電子事象と反射の波形の区別が難しいことが分かる。最初の信号入力から 900 nsec の間、次にやってくる信号を無視するように設定されているのはこのことを防ぐためである。ただし、このためにミューオンの崩壊事象に対するデッドタイムができてしまっている。

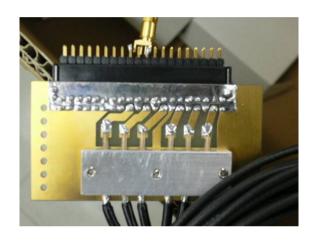

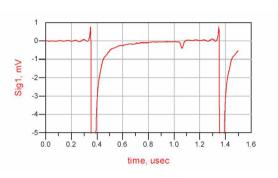

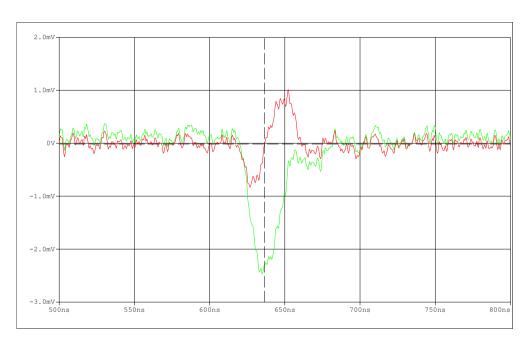

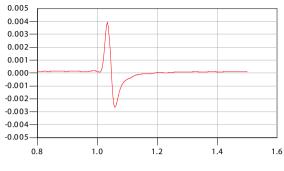

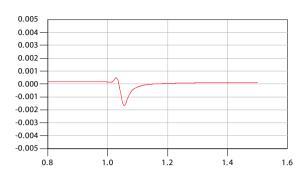

また、最近になって、同軸ケーブルと TKO のアナログ入力用の 40 ピンのコネクタとをつなぐ入力カード (図 3.4) の部分によってもインピーダンスの整合が悪化することが分かっており、たとえ ATM 側が理想的に  $50~\Omega$  で終端されていたとしてもこの入力カードによって、1.3~% の反射が起きることが分かった。図 3.5 が測定されたインピーダンスで行ったシミュレーションの結果であり、はっきりと反射波形を見て取ることができる。

したがって、精度の良いインピーダンス整合の実現のためにはこの入力カードも同時に改良する 必要がある。

さらに、この入力カードはチャンネル間のアイソレーションに関しても問題があり、最もアイソレーションの悪いチャンネル間では 0.5~% のクロストークを引き起こしていることも分かっており、そのことからも入力カードの改善が求められる。

反射係数の目標値としては数  $100~\mathrm{mV}$  の振幅の信号が引き起こす反射が無視できる程度が求められる。無視できるというのは、すなわち、ディスクリミネータにかからないことであるから、反射係数としては  $1/1000~(=-60~\mathrm{dB})$  程度が求められる。

図 3.4 入力カード。写真下側の部分に同軸ケーブルを半田で固定し、上側のコネクタを TKO のバックプレーンと接続する。

図 3.5 入力カードのインピーダンスの測定値を用いた反射のシミュレーションの結果。最初の入力電荷の約 700 nsec 後にある小さな波形が反射波形である。

アナログスイッチでのクロストーク 各 ATM が持つ ADC はそれぞれ一つであるから、マルチプレキサと呼ばれるアナログスイッチで各 TAC/QAC からの信号の切替えをしなければならないことになる。しかし、このアナログスイッチにおいて、チャンネル間のクロストークが起きてしまっているということが分かっている。

ADC の処理待機中の電流漏れ ADC が一つしかないということは他にも問題を引き起こしていて、AD 変換に 1 ヒットあたり 5.5  $\mu sec$  の処理時間がかかることで、電荷を保持してから、それが AD 変換されるまでの時間が、チャンネルによって違ってしまうことになる。例えば、全てのチャンネルに同時にしかも連続して信号が入力されるような事象を考えてみると、処理すべきチャンネル数は  $12 \times 2 = 24$  チャンネルであるから、最初のチャンネルが処理を始めてから最後のチャンネルの処理が終わるまでに  $5.5\mu sec \times 24 \sim 130\mu sec$  もの時間がかかってしまうことになる。これだけの時間がかかると、QAC と TAC で保持されていた電荷が少しずつ漏れていくという現象が見られ、遅く処理されるほど電荷が小さくなってしまうという効果が無視できなくなってしまう。そのために、現在では何番目に処理されたデータかという情報から漏れ電流に対する補正が必

要になってしまっている。

一つ前の問題と合わせて、これらは ADC 一つで全てのチャンネルの AD 変換を行うことに無理があることを示している。

電荷測定のダイナミックレンジ 電荷測定のダイナミックレンジは 約  $400~\rm pC$  である。これは  $1~\rm p.e.$  レベルでの十分な分解能を求めたところで決定されてしまっている。つまり、 $1~\rm hpc$  かっとなるようにすると、 $12~\rm hpc$  ではそのダイナミックレンジは  $0.1\times 2^{12}\sim 400~\rm [pC]$  となってしまう。序論でも述べたように高エネルギー領域の観測では、このダイナミックレンジは十分ではないことが分かっている。

現行システムの処理速度 これは現在は問題というわけではないが、より低エネルギーの観測を しようとしたときに限界に突き当たるのは明らかであるから、ここで述べておく。

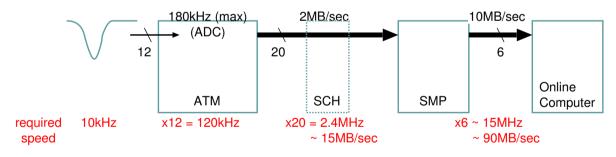

図 3.6 に現在のデータ収集の流れと各部の速度を示した。ここでは、全ての光電子増倍管から常に  $10~\mathrm{kHz}$  でヒットが発生する場合を考えてみる。まず、ATM は  $12~\mathrm{fr}$  サンネル入力を持つから、ATM に要求される速度は  $120~\mathrm{kHz}$  である。ATM の処理速度としては ADC の  $1~\mathrm{tr}$  ヒット当たり  $5.5~\mathrm{tr}$  を仮定したときに最大 約  $180~\mathrm{kHz}$  となる。この時点で既にぎりぎりの速度であるが、次に ATM から SMP までの転送速度を考えてみるとこれは実勢値で  $2~\mathrm{MB/sec}$  である。対して、要求される速度は ATM  $20~\mathrm{tr}$  たけってあるから  $2.4~\mathrm{tr}$  となる。 $1~\mathrm{tr}$  あたりのデータ量は  $6~\mathrm{Byte}$  であるから、要求される転送速度は約  $15~\mathrm{tr}$  の転送は現在のデータ転送速度では全く間に合わない。さらに、SMP からオンライン計算機への転送速度も同様に現在のシステムでは間に合わないことになる。

図 3.6 現在のデータ収集の流れと各部の速度

消費電力 現在の ATM の消費電力はおよそ 1 チャンネルにつき 4 W である。したがって、ATM だけでも 10000 チャンネルともなれば消費電力は 40 kW にもなる。一年中稼働していることを考えるとこの消費電力もできるだけ少なくする必要がある。

イベント番号のビット不足 表 3.1 にもあるように ATM が持つイベント番号は 8 ビットしかない。これを補うために GONG が 16 ビットのイベント番号を持ち、スパースデータスキャン時にまず GONG からイベント番号が読み出される形になっている。

しかし、超新星爆発などの高頻度の事象が起こった場合、SMP への読み出しが間に合わずに 8 ビットのイベント番号が一回りしてしまう恐れがある。カウンタが一回りしてしまうとどのデータ がどの事象のものかが分からなくなり、結局そのデータは使うことができなくなってしまう。こう いったことが起こらないように、新しいシステムでは ATM 内部にもイベント番号の全てのビットを持つべきである。

キャリブレーション作業の問題 現在のキャリブレーションは、光電子増倍管からの信号入力の入力カードをその都度外して、同じ入力経路から較正済みの信号源を入力するという方法で行われている。この作業を 1 万以上のチャンネルについて、全て行わなくてはならず、膨大な時間がかかってしまう。したがって、新しい ATM を開発するにあたっては、キャリブレーション作業を簡素化する必要がある。

## 4 新データ収集エレクトロニクスの概念設計

この章では新データ収集エレクトロニクスのシステムについて述べる。まず、数々の要請を満たすためのエレクトロニクスのシステム全体の設計に関する事項について議論する。また、今回のエレクトロニクスの刷新の中で最も大きな柱となるのが、フロントエンドエレクトロニクスである新ATM の開発である。まず、その概要を述べ、次にその ATM の中で中心的な役割を果たす QTCと TDC について述べる。

## 4.1 新エレクトロニクスへの要請

1 章でエレクトロニクスへの要請は既に述べられた。ここからは、具体的にその要請をどこで解決していくべきかについて述べていくことにする。以下では、フロントエンドで解決すべき課題とシステム全体で解決すべき課題に分けて、それぞれ述べていくことにする。

#### 4.1.1 フロントエンド (ATM) で解決すべき要請と解決策

フロントエンドエレクトロニクスである ATM が解決すべき要請と問題は以下のようになる。

- 1. 電荷測定のダイナミックレンジの拡大

- 2. 時間測定のダイナミックレンジの拡大

- 3. AD 変換の高速化

- 4. インピーダンスの不整合による反射の低減

- 5. 低ノイズ化

- 6. 低消費電力化

- 7. ATM がイベント番号の全てのビットを持つ

- 8. キャリブレーション作業の簡素化

インピーダンス整合の問題や低ノイズといった問題はもちろん重要なのであるが、時間測定のダイナミックレンジの拡大や AD 変換の高速化といった要請を満たすためには、AD 変換の方法を根本的に見直す必要がある。したがって、まずは AD 変換の方法について中心に述べていくことにする。

AD 変換の方法 現在の ATM では QAC と TAC により電荷と時間の情報をともに電荷へと変換し、それをボードにつき一つの ADC で AD 変換するという流れである。現在の ATM の問題のところでも述べたように、ボードにつき ADC が一つというのはいくつかの問題を引き起こしており、さらなる高速化のためにもこのシステムは限界があると考えられる。かといって、各チャンネルにそれぞれ高速な ADC を持たせるというのはコストがかかり過ぎる。電荷測定ダイナミックレンジの拡大のためには高ビットの ADC を使わなければならないから尚更のことである。したがって、ADC 以外の AD 変換の方法を探す必要がある。

ADC を用いない AD 変換の方法としては、電荷情報を時間へと変換するデバイスである QTC (Charge to Time Convertor) を用いる方法がある。QTC とは信号の電荷量を出力信号幅へと変換するデバイスで、その幅を  $\mathrm{TDC}^{*7}$ などで読むことで電荷量を AD 変換することができるものである。

QTC を用いるとすれば、あとは高分解能な TDC が必要である。さらに、データを取得する時間幅の拡大も要請されている。とくに、トリガーのかかる以前のヒットも取得できるようにするためには入力されたヒットの情報を常に AD 変換して、それをバッファに貯めておき、さらに、次のヒットを受け付けられるような仕組みが必要である。

そのどちらの要請も満たすような TDC が LHC の ATLAS 実験のミューオンドリフトチューブ MDT (Monitored Drift Tubes) のために開発されていることが分かった。その TDC は AMT (ATLAS Muon TDC) と呼ばれるマルチヒット TDC で、ちょうど数  $10~\mu {

m sec}$  の間の情報を内部 バッファにより保持することができ、しかも、同じチャンネルでもデッドタイム無く、次々と連続 する信号を AD 変換することが可能というものである。この TDC と QTC を組み合わせること により、上記のような仕組みが実現できるのではないかと考えられた。時間測定精度も  $60~{

m MHz}$  のクロックで使用することで  $0.15~{

m nsec}$  (RMS) となり、十分我々の要請を満たすものであった。 さらに、チップ  $1~{

m km}$  枚で  $24~{

m fine}$  チャンネルの入力を持ち、低コストかつ低消費電力であるという特長も持つ。

一方、QTC としては、以前に MQT (multi-ranging conversion of charge to time) という LeCroy 社により開発されたものが存在し、Belle 実験やスーパーカミオカンデの外水槽のエレクトロニクスでも使用されていたのだが、LeCroy 社が製造を中止したため、現在は手に入れることはできなくなってしまっているという状況であった。

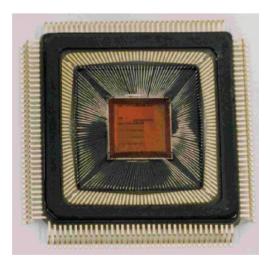

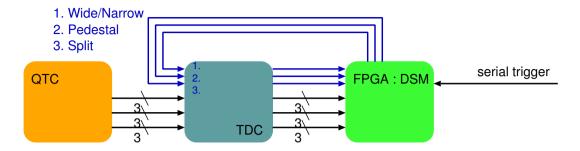

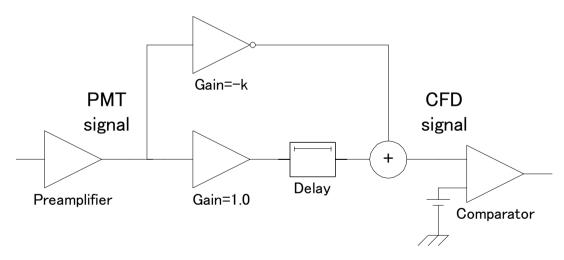

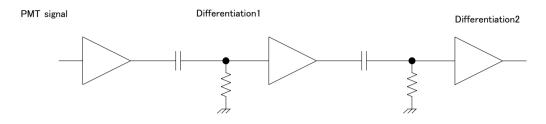

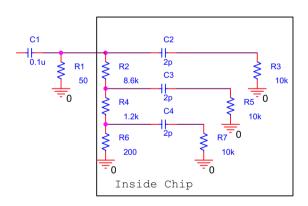

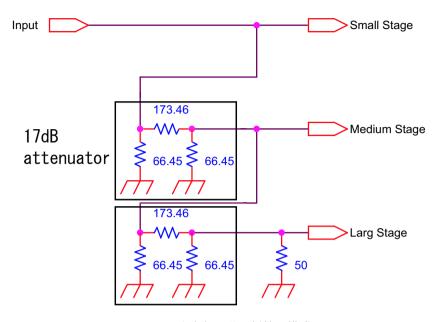

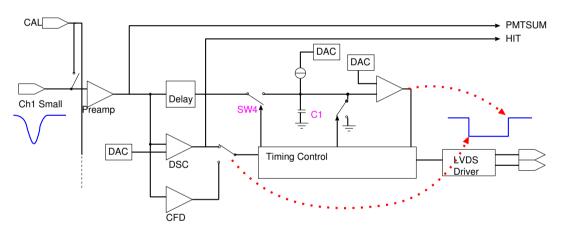

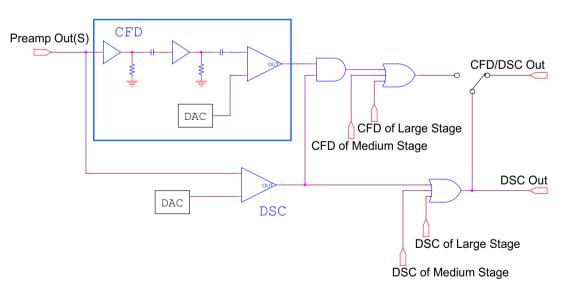

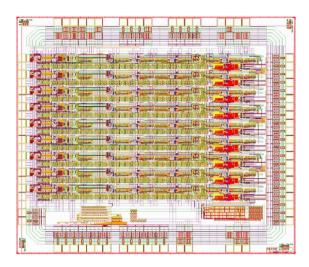

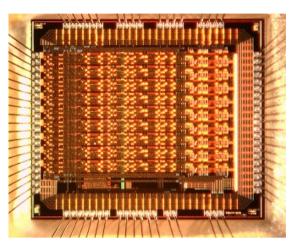

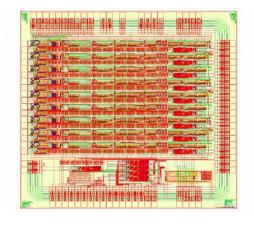

そこで、今回我々は新たに ASIC\*8として QTC を開発することにした。我々の開発する QTC の特徴は、ディスクリミネータを内蔵して、自らヒットを検出し、さらに積分ゲートを作って信号を積分するということにある。したがって、QTC と AMT の組合せにより、一つの信号で時間情報と電荷量を同時に AD 変換をすることができるようになると考えられる (図 4.1 参照)。また、信号のアナログ処理は全てこのチップ上で行われるから、低ノイズ化やインピーダンス整合などの要請はまず QTC で実現されるべきものである。さらに、QTC で高速な処理を実現することにより AD 変換の高速化が図られる。

一方、電荷測定のダイナミックレンジの拡大に関しては、一つのチャンネルにつき三つのゲイン のサブチャンネルを用意することで実現することとした。

<sup>\*&</sup>lt;sup>7</sup> Time to Digital Convertor の略。

<sup>\*8</sup> Application Specific Integrated Circuit の略。特定の用途のために設計された IC のこと。

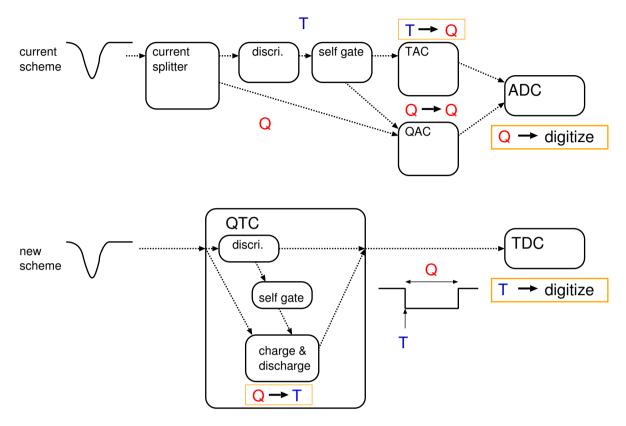

図 4.1 現在の AD 変換と新しい AD 変換の流れ。これまでの AD 変換とは逆に時間、電荷情報ともに時間に変換して、TDC で AD 変換を行うことになる。

図 4.2 QTC プロトタイプ パッケージ写真

## 4.1.2 データ収集システム全体で解決すべき要請と解決策: 高速化

要請のところで何度も述べられたように、システムの高速化は最も重要な課題の一つである。高速化はシステムのどの要素が欠けても実現されないから、これは ATM だけを高速化すれば済む問題ではない。

- 一口に高速化と言っても、要請されることは異なっており、次の3種類に分けられる。

- 1. AD 変換の高速化

- 2. 常時入力される全てのチャンネルの 10 kHz のヒットを処理する

- 3. 約 10 sec 間の 100 kHz の超新星爆発の信号をデッドタイム無く処理する

最初の AD 変換の高速化はもう既に述べられたので、ここでは後の二つについて議論する。

最初に 2. の要請を満たすためには何が必要かを考えてみる。まず、現在のデータ収集システムでボトルネックとなっているのは、前の章でも述べたように ATM からオンライン計算機までのデータ転送速度が要請よりも一桁小さいと言うことである。この部分の高速化に関しては現在までのところ二つの解決策が考えられている。

- 新しく SCH を開発し、SMP を介さずに SCH からオンライン計算機へと接続する。また、 TKO バスのプロトコルを 2 倍に高速化する。

- ATM に 100BASE-T イーサネット読み出しのための拡張ボードを付け、ATM とオンライン計算機とを直接接続する

新しい SCH の開発では現在の約 8 倍のデータ転送速度が、 $100 \mathrm{BASE-T}$  イーサネット読み出しでは約 25 倍のデータ転送速度が期待される。これらの詳細については 4.4 で述べることとする。ただし、これは ATM からオンライン計算機までのデータ転送の話であり、オンライン計算機での処理速度や計算機間の転送速度などはまた別に改良を加えなくてはいけない。

次に、3. の  $100~\rm kHz$  の超新星爆発による事象の取得について考える。序論でも述べたように超新星爆発ニュートリノのエネルギーは  $10~\rm MeV$  程度であるので、約  $1~\rm T$  万本ある光電子増倍管の中でヒットがあるのは、その中の  $1~\rm \%$  の  $100~\rm t$  在程度である。したがって、一つのチャンネル当たりに換算すると、 $1~\rm kHz$  程度のヒットにしか相当しない。これは、一つ前の要請である  $10~\rm kHz$  のヒットを常時とり続けることと比べると十分小さいもので、常時  $10~\rm kHz$  のヒットを取得するという要請が満たされているならば、自動的に  $100~\rm kHz$  の超新星爆発の信号に対しては十分高速であると考えることが出来る。

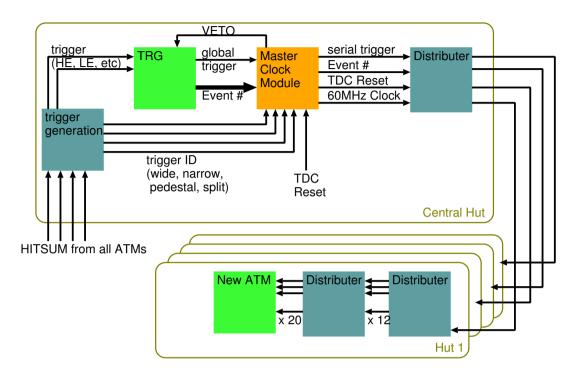

## 4.2 新データ収集エレクトロニクスの全体図

ここでは、新しいデータ収集エレクトロニクスの全体図について述べる。ただし、章題にもあるように現段階ではまだ「概念設計」という段階に過ぎない。各項目の開発の進み具合はまちまちであり、大きな選択肢が未だに残されている箇所もある。

最も大きな選択肢としては、トリガーにかかわらず全てのヒットをデータ収集系で取得するか、否かである。この新しいエレクトロニクスのインストールの日程としては、次期長基線ニュートリノ振動実験 T2K 実験が始まる 2009 年の一年前である 2008 年の始めに行う予定である。そのときにどういったシステムを選択するかは、今後の開発の進み具合で決定されるのだが、ここでは、その両方の場合のシステムについてその概念図を示す。

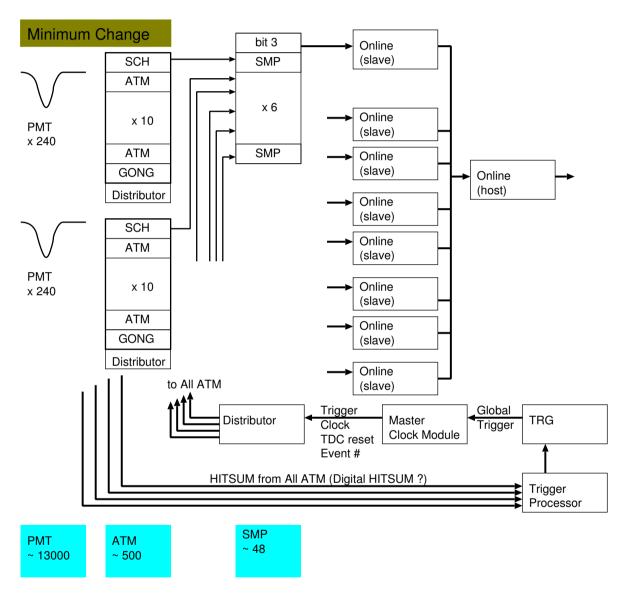

## 4.2.1 最小限の改良: ATM だけを新しくした場合

まずは、ATM だけを新しくした場合の全体図を図 4.3 に示す。この場合はシステムとしては現状と殆ど変わりは無く、ATM  $\rightarrow$  SCH  $\rightarrow$  SMP  $\rightarrow$  Online Computer というデータの流れは同じである。ただし、大きな変更点としてはシステム全体を一つのクロックで動かすということがある。これは新しいシステムを動作させるにはなくてはならないものとなっている。他には、トリガーの生成を現在の HITSUM 信号のアナログ和をとるシステムからデジタルで処理するシステムへと変更することも考えられている。このトリガーの改良については 4.5 で述べる。さらに、小さな変更としては TRG モジュールを新しくすることにより、これまで 16 ビットだったイベント番号が 32 ビットまで拡張されるといった変更点もある。

システム全体を一つのクロックで動かすのは次のような理由がある。

- 異なる TDC 間、ATM ボード間でのチャンネル間の相対時間差を最も良い精度で測定する ため

- もし、ATM がそれぞれ独自のクロック持っていた場合、異なるボード間でのヒットの相対時間差は、TDC から出力される生のカウントからは分からないことになる。トリガーの入力は全ての TDC に同時に入力されることになるから、この時間を同時に各TDC で測定すれば良いのだが、そうした場合の相対時間差の測定精度には、次の式のようにトリガー時間の測定精度の項が入ってきてしまう。例えば、独立したクロックで測定された  $t_1$  と  $t_2$  の相対時間差をトリガー時間  $t_{\rm trg}$  を基準として測ろうとすると、その測定精度は次のようになる。

$$\Delta(t_1 - t_{\text{trg}}) = \sqrt{\Delta t_1^2 + \Delta t_{\text{trg}}^2}$$

$$\Delta(t_2 - t_{\text{trg}}) = \sqrt{\Delta t_1^2 + \Delta t_{\text{trg}}^2}$$

$$\Delta(t_1 - t_2) = \Delta \{(t_1 - t_{\text{trg}}) - (t_2 - t_{\text{trg}})\} = \sqrt{\Delta t_1^2 + \Delta t_2^2 + 2\Delta t_{\text{trg}}^2}$$

(4.1)

一方、全ての TDC を同一のクロックで動かせば、相対時間差は TDC の出力される 生のカウンタの値を比較することで測定が出来るので、トリガー時間の測定精度の項は は行ってこない。

ただし、このためには、全ての TDC の内部のカウンタを同時にリセットし、同期化することも必要となる。

一つのクロックで全ての TDC を動作させれば、TDC のカウント値 → 実時間のキャリブレーションを全てのチャンネルで行う必要が無くなり、もとのマスタークロックの周波数を

精度良く測定しておけば良いことになる

- モジュール間で情報をシリアル転送\*9できるようにするため。

- これまでのトリガーでは、トリガー生成時には HE や LE といった種類があったものの ATM へはトリガーの種類の情報は伝えられていなかった。新しい ATM ではそのトリガーの種類によって動作を変える必要がある。したがって、トリガーの種類の情報も全ての ATM へと伝えることが必要となった。それらの情報をパラレル転送しても本質的に問題は無いが、信号線の本数を減らすため、シリアル転送を採用した。イベント番号に関しても、同様にシリアルで転送し、32 ビットのイベント番号を 4 本の信号線で転送する。全てのボードが同じクロックで動いていることで、データのシリアル転送は容易になる。

- さらに、新しいシステムではトリガー生成のための HITSUM をデジタルで処理する ことを考えている。それは、1 クロックの間に何ヒットがあったかをボードごとに出力 し、その和でトリガー生成の判断をするものである。このシステムが動くためにも全て のボードが同一のクロックで動作している必要がある。

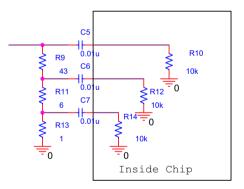

クロックやトリガー、イベント番号、TDC のリセットの分配のためには新しいモジュール (Master Clock Module と呼ぶ) が必要となるが、その開発を現在進めているところである。詳しくは 6 章にて述べる。

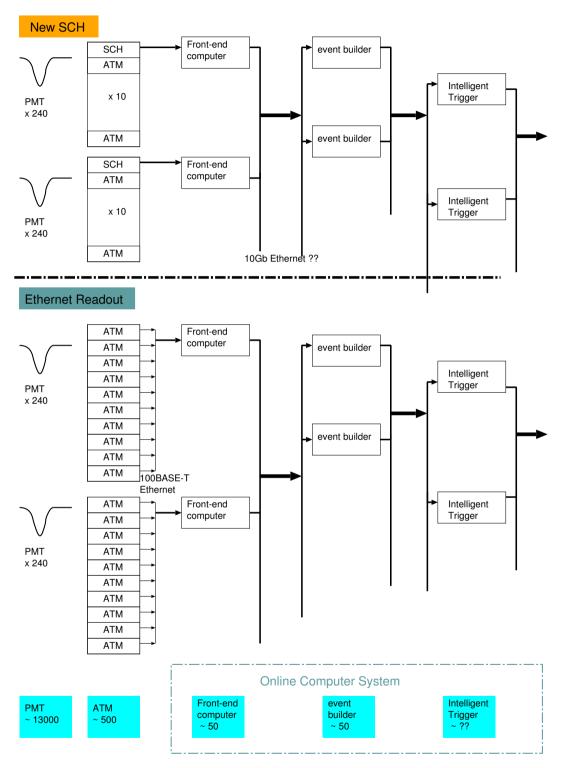

#### 4.2.2 常時全てのデータをとり続ける場合

次にトリガーにかかわらず、常時全てのヒットをとり続ける場合のシステムについて説明する。 図 4.4 が全てのヒットをとるために考えられたシステムの概略である。図にもあるように現在の ところ二つの選択肢があり、一つは SCH を新しく開発すること、もう一つは各 ATM に拡張ボードを付け、そこから直接イーサネット読み出しでオンライン計算機へとつなぐ方式である。

どちらの方式の場合でも最早 SMP は使われないことになる。また、この場合には膨大なデータ量を処理するオンライン計算機の大幅な拡充とソフトウェアの改良が必要となり、それらの検討はまだこれからという段階である。図 4.4 中の "Front-end computer" はおよそ 1 クレート (= ATM ボード 10 枚 = 240 チャンネル) につき 1 台程度となり、各ヒットの並べ替えなどを行う。 "event builder" も同程度の台数で、各ハットからのデータを組み合わせて、"Intelligent Trigger" に転送する。さらに "Intelligent Trigger" でデータの選別を行うことになる。ここでどの程度 "Intelligent" な選別を行うかによって、ここに必要な計算機の数は決まってくる。

システム全体としてのデータ処理速度に関してはまた 4.4 で詳しく扱うこととする。

$<sup>^{*9}</sup>$  一本の信号線を使って 1 クロック毎に 1 ビットずつデータを転送する方式。対してパラレル転送とは、複数の信号線を使って並行にデータを転送する方式のこと。

図 4.3 ATM だけを改良した場合のデータ収集システム。殆ど現行のシステムと変わらないが、トリガーやイベント番号、クロックの分配のために新しいモジュールが加わる。

図 4.4 全てのヒットを常時取得する場合のシステムの全体図。二つの大きな選択肢についてそれぞれ示した。オンライン計算機の数などの見積りは概算であり、詳細な見積りはまだこれからである。

#### 4.3 新 ATM

新しい ATM への要請に関しては、既に 4.1.1 で示した通りである。それらの要請を満たすため に新 ATM では QTC と TDC による信号の AD 変換というシステムを採用することまでは既に 述べた。以下では、そのシステムをどのように構築するかなどの具体的な ATM のデザイン、また、その各部の詳細について述べていくこととする。

また、開発にかかる時間の短縮などのために現在存在する資源をできるだけ活用するという考えから、新しい ATM も基本的には TKO 規格で開発される。

#### 4.3.1 信号の流れ

ここでは、光電子増倍管からの信号がどのように処理されるのかの概要を順を追って説明する。 大まかなブロック図を図 4.5 に示した。

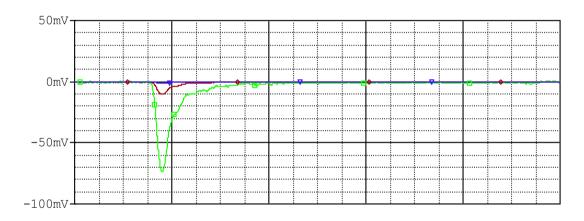

まず、 $70~\mathrm{m}$  の同軸ケーブルを伝ってきた光電子増倍管からの信号は、入力カードを経て、 $\mathrm{TKO}$  のバックプレーンに二つある  $40~\mathrm{U}$ ンのコネクタを通して  $\mathrm{ATM}$  へと入力される。 $\mathrm{ATM}$  へと入力された信号はまず  $\mathrm{QTC}$  へと入力される。ただし、 $\mathrm{QTC}$  へと入力される前に信号は適当に抵抗分圧されて、 $3~\mathrm{DOD}$  つのレンジへと分けられる。それと同時に、高精度のインピーダンス整合が行われる。また、新  $\mathrm{ATM}$  は現在の  $2~\mathrm{GE}$  倍の  $24~\mathrm{EV}$  チャンネルの入力を持つから、 $3~\mathrm{EV}$  チャンネルの入力を持つ  $\mathrm{QTC}$  はボードー枚につき  $8~\mathrm{V}$  枚が必要となる。

QTC は内部にディスクリミネータを持ち、入力された信号がその閾値を越えると処理を開始する。QTC は一つのチャンネルにつき 3 つのレンジを持ち、どのレンジに相当する信号であろうと全てのレンジで信号を出力するので、1 チャンネルでヒットがあると QTC では実質 3 チャンネル 分の出力を出す。それと同時に QTC からはチャンネルごとに HIT 信号が出力される。その HIT 信号を元に ATM 内部で HITSUM が作られる。その HITSUM 信号が中央のセントラルハットのトリガー生成部に送られ、トリガーが生成されるというのは現在のシステムと同じである。

QTC からの出力は LVDS\* $^{10}$ レベルで直接 TDC (AMT) へと入力される。TDC では QTC からの入力を受けて、入力された信号のエッジの時間と種類 (立ち上がりエッッジか立ち下がりエッジか\* $^{11}$ ) を内部バッファに記録する。この処理はグローバルなトリガーの入力によらず常に行われている。そして、外部からトリガーが TDC へと入力されると、TDC は 12 ビットの TDC 内部のイベント番号、及びそれまでに入力された信号のチャンネルとエッジの時間を出力する。TDC への入力は 1 ヒットにつき 3 つのレンジ分の 3 チャンネルの入力がある。したがって、TDC からも 3 チャンネル分のエッジ情報が出力される。また、TDC は 24 チャンネルの入力をもつから、QTC 2 枚分 (=  $3 \times 3 \times 2 = 18$  チャンネル)のヒット情報を処理することが出来るので、ATM はTDC を 4 枚持つことになる。

TDC から出力された各エッジの時間情報は DSM (Data Sort Mapping) と呼ばれる

$<sup>^{*10}</sup>$  Low Voltage Differential Signaling の略。 $+1.25~\mathrm{V}$  を中心とした振幅約  $0.3~\mathrm{V}$  の差動信号。

$<sup>^{*11}</sup>$  差動信号なのでどちらを立ち上がりと呼ぶかは定義によるが、最初のエッジを立ち上がりエッジと呼ぶことにする。

$\mathrm{FPGA}^{*12}$ によって読み出される。 $\mathrm{DSM}$  は  $\mathrm{TDC}$  一枚につき、一枚が用意される。したがって、ボードー枚では 4 枚の  $\mathrm{DSM}$  を持つことになる。 $\mathrm{DSM}$  では次のような処理が行われる。

- 1. TDC からのエッジ時間の情報をチャンネルごとに並び替える。

- 2. トリガーの種類によっては、ある時間より前のヒットの情報を捨てる

- 3. (立ち下がり時間) (立ち上がり時間) の引き算を行い、QTC 出力信号幅を求める

- 4. QTC 出力信号幅の値から、飽和しているレンジを探して、3 つのレンジの中からどのレンジの幅の情報を使うかを決定する。この時点で各チャンネルの電荷、時間情報は AD 変換されたことになる。

- 5. チャンネルごとの QTC 出力信号の立ち上がり時間と幅とレンジの情報、さらにイベント番号の情報を SIC (System Interface Control) と呼ばれる FPGA へと出力する。

SIC には 4 枚の DSM からの情報が集められる。外部から入力される 32 ビットのイベント番号を持っているのはこの SIC である。そして、 SIC は TKO バスなどを介して、SCH もしくは イーサネット読み出しのための拡張ボードとのデータのやりとりを行う。そのデータ転送には TKO プロトコル、もしくは、新 SCH や拡張ボードとの通信では高速化した TKO プロトコルを用いる。外部からのトリガー、TDC のリセット信号なども一度この SIC を通してから、全てのDSM へと分配するという形をとる。また、瞬間的に高頻度な事象が発生して、SIC から外部への転送速度が間に合わなくなったときのために 1 MByte 程度の FIFO\* $^{13}$  を搭載する。1 ヒットあたりのデータ量は現在の ATM と同じで 6 Byte となるから、  $1.7 \times 10^5$  のヒットまでは貯めておくことができる。FIFO のサイズとしては現在の ATM の 500 倍となるが、チャンネル数は 2 倍に増えているから、実質的には 250 倍となる。

各部の詳細については、以下に挙げる章節において説明されている。

- QTC の入力部の抵抗分圧 · · · 5.1.4

- QTC 内部での処理 · · · 5.2

- TDC での処理 · · · 4.3.4

- FPGA におけるデータ選別と 1 ヒットのデータ構造 · · · 4.3.5

- 高速化 TKO プロトコルを含む高速化の詳細 · · · 4.4

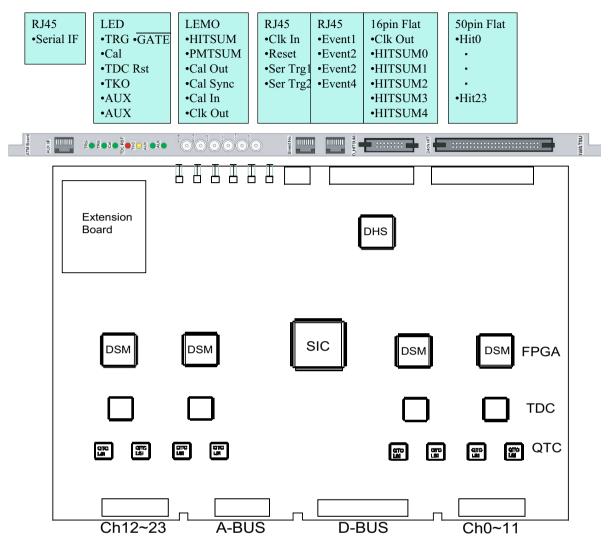

#### 4.3.2 信号入出力

ここでは、信号の入出力について一通り述べておく。さらに、これまで触れられなかった信号に ついても簡単に説明を行う。

図 4.6 が新 ATM のフロントパネルのデザインである。

<sup>\*&</sup>lt;sup>12</sup> Field Programmable Gate Array の略。書き換え可能なゲートアレイの一種。

$<sup>^{*13}</sup>$  First In First Out の略。先に書き込んだデータから先に取り出される方式またはそういった方式のメモリのこと。ここでは、実際には高速な SRAM を搭載し、それを SIC が FIFO として制御する。

図 4.5 新 ATM ブロック図。青色の線で光電子増倍管からの信号の処理の流れを図示した。

入力カード 現在の ATM の入力カードはインピーダンスの整合とアイソレーションの悪化を もたらしていたことは 3 章で述べられた。その改善のため、新しい入力カードの製作も ATM の 開発と並行に進められている。現段階では、多層板の内層を信号ラインとして使うストリップライ ンという方式でより特性の良い入力カードを作ろうとしているところである。

クロック、トリガー、イベント番号入力、TDC リセット Master Clock Module から分配されるこれらの信号の伝送にはカテゴリー  $5\mathrm{E}$  のイーサネットケーブルを使用する。そのための RJ-45 のモジュラジャックが 2 つ用意されている。

HITSUM まず、現在のシステムと互換性を持つためにアナログの HITSUM 出力が LEMO コネクタで用意されている。また、HITSUM を 5 ビットのデジタル信号 (Digital HITSUM) とし

図 4.6 新 ATM フロントパネルとボード上の配置

て送るための 16 ピンのフラットケーブルがつなげるようになっており、この出力からは同時にクロックも出力される。このデジタルの HITSUM を作るために一つ DHS (Digital Hit-Sum) と呼ばれる FPGA が使われる。さらに、それぞれのチャンネルの個別の HIT 信号を 50 ピンのフラットケーブルに出すこともできるようになっている。出力レベルは LVDS で各 QTC の HIT 信号がクロックで同期をとられずにバッファを介して出力される。

PMTSUM この出力は現在の ATM と全く同じ働きを持つもので、24 チャンネルの波形のアナログ和を出力する。

キャリブレーション関係 ここでは、新しい ATM でのキャリブレーションに必要な入出力について一通り述べておく。

"Cal In"とは外部のキャリブレーションパルサーを用いるための入力である。ここから入力し

た信号は全ての QTC のキャリブレーション用専用入力チャンネル (CAL) から入力され、ボード内の全てのチャンネルのキャリブレーションを行うことができる。

"Cal Sync"はキャリブレーションを行っていることを示す信号で、キャリブレーションパルサーと同期した信号である。"Cal Out"はキャリブレーション入力として入力されている信号を出力する端子で、キャリブレーションに使われている信号のモニターのために使われる。

イーサネット読み出し 最後に図 4.6 中の左端に位置する RJ-45 のモジュラジャックについて であるが、これはイーサネット読み出しのための拡張ボードのためのものである。

さて、これまではどのようにして光電子増倍管の信号の時間と電荷の情報を AD 変換して外部へと転送するかの流れを述べた。しかし、ATM への数々の要請が具体的にどのように解決されているのかはまだ、明らかになっていない。ATM への要請のうち多くは QTC への要請となり、QTC 自体の議論が必要となるので、それらは次章で述べることになるが、以下では、時間測定ダイナミックレンジの拡大と ATM の処理速度に関して述べていくことにする。そのために、まずはQTC と TDC の動作に関して理解が必要なので、それらについて述べることにする。

#### 4.3.3 QTC の処理速度

ここでは、QTC の処理速度について理解するために、QTC の仕組みを簡単に述べる。

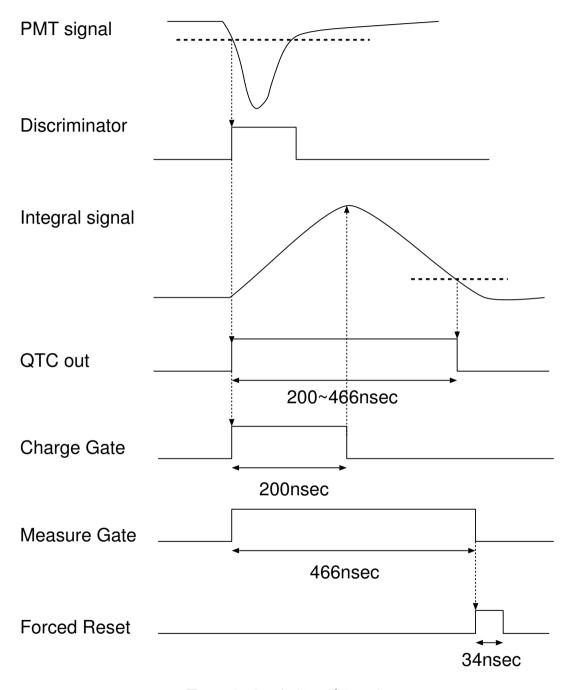

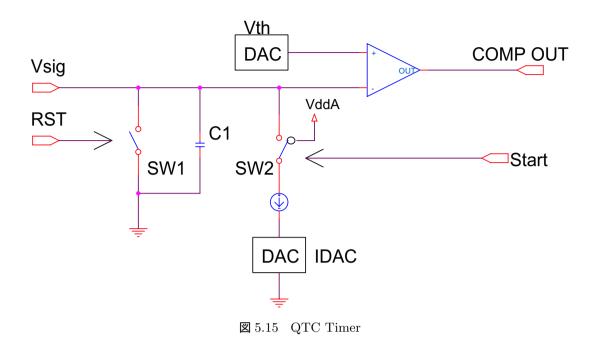

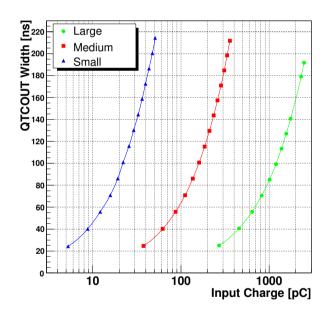

まず光電子増倍管などからの信号の入力が内部のディスクリミネータの閾値を越えると、QTC からの出力信号が立ち上がる(QTC から出力される信号の最初のエッジを立上りエッジと呼ぶこととする)。したがって、この立ち上がり時間は信号の入力の時間を表すことになる。次に、信号の立上りから、ある決められた積分ゲート時間の間、内部では入力信号の電荷を積分していく。その積分ゲートが終わると、次にある定電流でそれを放電していく、放電ゲートが始まる。この放電により、積分された信号の電圧がある閾値を下回ると出力信号が立ち下がる。したがって、この出力信号の幅は入力信号の電荷の情報を持つことになる。QTC の処理速度の議論に必要となるのはこの(積分ゲート + 放電ゲート)の時間(この時間を測定ゲートと呼ぶことにする)である。この測定ゲートの間に放電が終わらなかったときには強制的な放電が始まり、出力信号も強制的に立ち下がってしまう。つまり、このときそのチャンネルは「飽和」していることになる。したがって、あるチャンネルが飽和しているかどうかは出力信号幅がこの測定ゲートの大きさであるかどうかで判断ができる。

また、一つの信号の処理にかかる時間もこの測定ゲートの時間で決まり、測定ゲートは現在のところ 500 nsec という設定にしようと考えている。入力された信号の放電がいくら早く終わってしまおうとも、この 500 nsec の測定ゲートの間は次の信号入力を受け付けないようになっている。したがって、QTC の処理速度は最大で 2 MHz であるということができる。

この QTC の仕様の詳細、性能評価の結果については、次章で詳しく述べられる。

## 4.3.4 AMT (ATLAS Muon TDC)

AMT はこの章の最初でも述べられたように ATLAS 実験用に開発されたマルチヒット TDC である。その主な仕様は表 4.1 のようになっている。

表 4.1 AMT の主な仕様

時間分解能 0.5208 nsec/Count (60 MHz クロック動作時) 時間測定精度 0.150 nsec (RMS) ダイナミックレンジ 17 bit (13 bit coarse counter & 4bit fine counter) 入力チャンネル数 24 チャンネル 入力クロック周波数 10 ~ 70 MHz 非線型性 < 80 psec (integral & differential) < 15 mW/チャンネル (< 360 mW/chip)消費電力 信号入力レベル LVDS 電源電圧  $3.3 \pm 0.3 \text{ V}$ プロセス  $0.3 \ \mu m \ CMOS$ パッケージ 144 pin QFP

☑ 4.7 AMT (ATLAS Muon TDC)

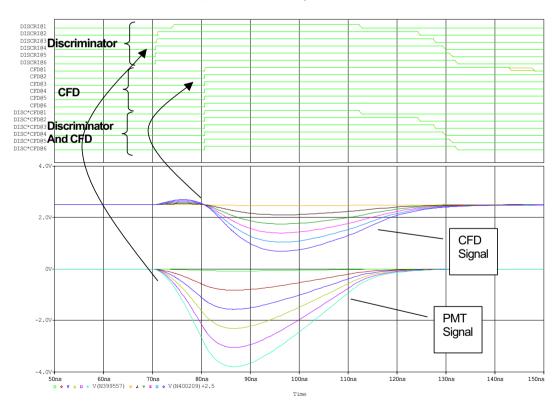

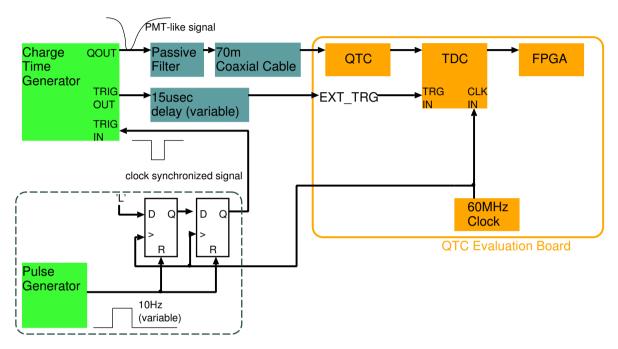

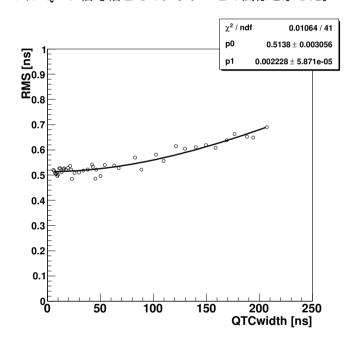

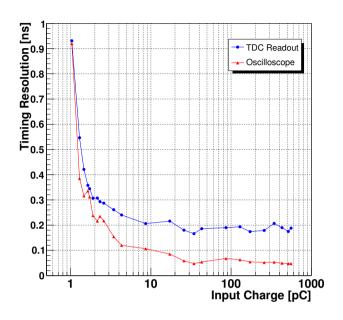

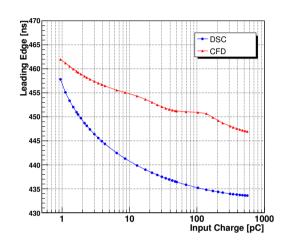

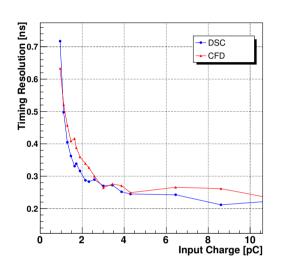

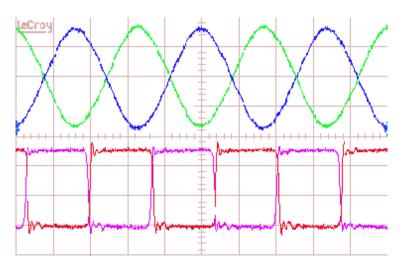

ATLAS 実験ではこの TDC を  $40~\rm MHz$  で動作させるが、我々の実験ではもう少し時間分解能を良くするため  $60~\rm MHz$  のクロックで動作させる。それにより、 $1~\rm h$ ウントあたり  $520.8~\rm psec$  の分解能、RMS では  $520.8/\sqrt{12}=150~\rm [psec]$  の時間測定精度が得られることになる。これは我々の要請を満たすものである。次章の QTC の性能評価に用いた評価基板上にはこの AMT が搭載されており、QTC の性能評価に兼ねて AMT の動作評価も行ってきた。これまでのところ  $60~\rm MHz$

でも問題無く動作している。ただし、供給電圧は標準より 10~% 高い  $+3.6~\mathrm{V}$  に設定する。このようにした経緯は次章の 5.4.1 で述べられる。

AMT の詳細は [13] に述べられているが、ここでは、以降の議論に必要となるいくつかの点について説明をしたいと思う。

AMT における内部カウンタ AMT 内部ではまず入力された  $60~\mathrm{MHz}$  クロックを  $\mathrm{PLL}^{*14}$ で  $2~\mathrm{em}$   $120~\mathrm{MHz}$  にする。内部にはこの  $120~\mathrm{MHz}$  の周波数をもつ  $16~\mathrm{Em}$  段の非対称なリング発振器があり、これにより  $16~\mathrm{Em}$  個の少しずつ位相のずれたカウンタを作る。以上により、入力されたクロックの  $32~\mathrm{Em}$  信の周波数のカウンタが作られる。したがって、実際の内部カウンタの実効周波数は  $60~\mathrm{[MHz]} \times 32 = 1.92~\mathrm{[GHz]}$  である。これによって、AMT では  $0.52~\mathrm{nsec/Count}$  の時間分解能を有することになる。

24 あるチャンネル入力のエッジの時間はこのカウンタにより測定される。ただし、トリガーマッチングはもとの入力クロック周波数の  $60~\mathrm{MHz}$  で行われるから、トリガーの時間情報は  $16.7~\mathrm{nsec}$  の分解能しか持たないのだが、我々の用途ではトリガー時間の精度はそれほど必要としないので特に問題は無い。

AMT における内部バッファ AMT は内部にバッファを持ち、ヒットの情報をトリガーが入力 されるまで保持することができ、かつ、エッジの時間の測定、トリガーマッチング、外部への読み 出しなどを並行して行うことができるようになっている。AMT の内部バッファの構造とそれぞれ の役割について以下に説明する。

## 1. Channel Buffer

それぞれのチャンネルで測定されたエッジの時間情報はまず各チャンネルに用意された Channel Buffer に書き込まれる。この Channel Buffer では 4 つまでのエッジの時間情報 を貯めておくことができる。それらのヒット情報はクロックと同期して、次の L1 Buffer へ と書き込まれる。

どれくらい短い間隔でくるエッジを測定できるかは、この Channel Buffer への書き込み時間で決定されることになる。例えば、5 nsec 幅の信号が 5 nsec 間隔で連続で入力されても AMT は 4 つあるエッジの情報を正しく測定することができ、これは我々の用途にとって十分な速度であるということができる。

## 2. L1 (Level 1) Buffer

Channel Buffer に書き込まれたヒット情報はチャンネル情報などを付加された後に、L1 Buffer へと書き込まれることになる。L1 Buffer では、256 個のエッジの時間情報を蓄積することができる。L1 Buffer からの読み出しはランダムアクセスであり、トリガーが入力されると、その都度トリガーにあったヒットが探し出され、読み出されていく。

#### 3. Trigger FIFO

<sup>\*&</sup>lt;sup>14</sup> Phase Locked Loop の略。入力信号と基準周波数が等しくなるように出力信号に負帰還をかける回路。周波数の安定や周波数を整数倍にするために用いられる。

トリガーが入力されるとそのトリガーの入力時間とイベント番号が Trigger FIFO に書き込まれる。Trigger FIFO には 8 つのトリガーまでの情報を貯めておくことができる。トリガーが入力されるとそのトリガー入力時間を基準にあらかじめ設定されたトリガーマッチングの条件に当てはまるエッジの情報を L1 Buffer から探し出して、Readout FIFO へと書き込む。

#### 4. Readout FIFO

L1 Buffer から読み出されたエッジの時間情報は最後に Readout FIFO に貯められる。ここでは、64 のエッジの時間情報やヘッダー、トレイラーなどのデータを保持することができる。

Readout FIFO が一杯になってしまったときにどのような処理を行うかは、いくつか選択 肢があり、レジスタ設定により決めることができる。

- Readout FIFO に空きができるまで、トリガーマッチングを行わない。(データは捨てない。)

- Readout FIFO が一杯、かつ、L1 Buffer が殆ど一杯になったときに次のトリガーマッチングを行わず、さらにイベント番号などの情報を持つヘッダーとトレイラー以外のデータを全て捨てる。

- Readout FIFO が一杯になると同時にヘッダーとトレイラー以外の全てのデータを捨てる。

スーパーカミオカンデにおける使用では、AMT で処理仕切れないほどのデータが短時間に やってきた場合には、一度取ったデータを捨てることはせずに、バッファが一杯になってし まったら、それ以降のデータを受け付けないようにするという方法にするべきである。した がって、上に挙げた選択肢のうち、一つ目の設定を選択することになる。ただし、そのよう な異常な頻度のヒットの入力が続いた場合、この設定では 1 枚の AMT の測定が全く停止 してしまうことが考えられるのだが、AMT で扱えないようなデータ量はその後の部分でも 処理できない部分が出てくると思われるので、AMT が 1 枚止まってしまう事自体は問題と はならないと考えている。

最終的に AMT から出力されるデータの構造は表 4.2、4.3、4.4 などのようになる。典型的な 1 イベントのデータでは、まずヘッダーが出力され、その間に全てのチャンネルのヒット情報、最後 にトレイラーが出力される。AMT の持つイベント番号は 12 ビットであり、各エッジの時間情報 は "Coarse Time" の 12 ビットと "Fine Time" の 5 ビットを合わせて 17 ビットである。

また、AMT からのデータの読み出しは、パラレルとシリアルの両方が可能であるが、我々の用途では、処理のより容易なパラレル読み出しの方を選択する。

#### AMT の出力データ構造

表 4.2 Single Measurement Data (通常のエッジの時間情報)

| 31 | 30 | 29 | 28 | 27-24  | 23-19 | 18   | 17    | 16-5        | 4-0       |

|----|----|----|----|--------|-------|------|-------|-------------|-----------|

| 0  | 0  | 1  | 1  | TDC ID | Ch    | Edge | Error | Coarse Time | Fine Time |

表 4.3 TDC header (Bucnh ID とはトリガー入力時の Coarse Time (60MHz) のカウント値)

|   | 31 | 30 | 29 | 28 | 27-24  | 23-12    | 11-0     |

|---|----|----|----|----|--------|----------|----------|

| ĺ | 1  | 0  | 1  | 0  | TDC ID | Event ID | Bunch ID |

表 4.4 TDC trailer (Word count とは TDC から出力される 1 イベント中のデータの数)

| 31 | 30 | 29 | 28 | 27-24  | 23-12    | 11-0       |

|----|----|----|----|--------|----------|------------|

| 1  | 1  | 0  | 0  | TDC ID | Event ID | Word Count |

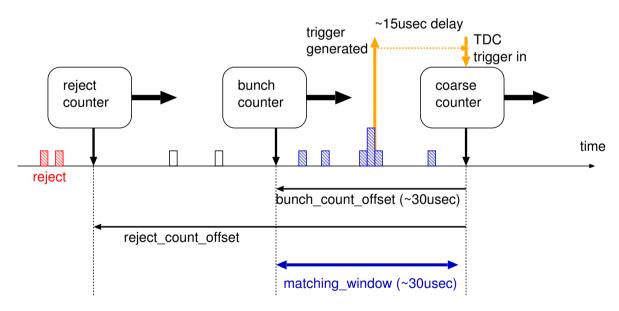

AMT におけるトリガーマッチング ここでは AMT を用いて、どのようにしてトリガーの前後数  $\mu sec$  のヒットを取得するかを説明する。

トリガーマッチングには3種類のカウンターが関わっている。

- coarse counter

- bunch counter

- reject counter

イメージとしては、これらのカウンターが図 4.8 にあるようなオフセットを持って、同じ速さで回っていると考えればよい。ただし、これらのカウンタは 12 ビットのカウンタであり、入力クロック周波数と同じ  $60~\mathrm{MHz}$  で回っている。

あるチャンネルでエッジが検出されると、その時点での coarse counter のカウンタの値が ラッチされ、ラッチされたカウンタの値がエッジの時間となる。その coarse counter よりも bunch\_count\_offset と呼ばれるだけのオフセットを持って遅れて回っているのが、bunch counter である。トリガーが入力されると、そのときの bunch counter の値がラッチされ、それがトリガー の時間 (Bunch ID と呼ばれる) になる。

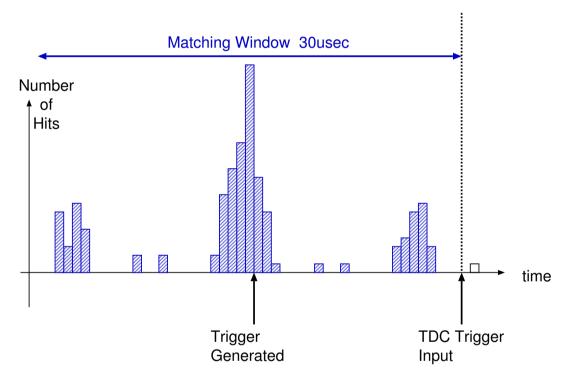

AMT におけるトリガーマッチングとは、トリガー時間を基準とし、そこから数えて  $matching\_window$  と呼ばれる幅に入っているカウンタの値を持つエッジを、 L1 Buffer の中から選び出し、さらに、Readout FIFO へと書き出すことである。

それでは、我々の用途のためにはどのように設定すれば良いか。まず、AMT としてはトリガーの後のヒットを得ることはできないから、外部でトリガーが生成してから、AMT へと入力するまでに約  $15~\mu sec$  程度の遅延を入れる必要がある。さらに、bunch\_count\_offset と mathching\_window をともに約  $30~\mu sec$  に設定してやれば、トリガーの生成から前後  $15~\mu sec$  の信号が matching\_window に入り、その間のヒットの情報が取得できることになる。これにより、ATM へと要請された時間

ダイナミックレンジの拡大は実現されることとなる。

ただし、これらのカウンタ  $(12\ \text{Uy}\ \text{F})$  が一回り  $(60\ \text{MHz}$  クロック動作時では 約  $70\ \mu\text{sec}$  ) してしまったときに、古いヒット情報が L1 Buffer に残っていると、古いヒットと新しいヒットとの区別がつかなくなってしまう。それを防ぐために用意されているのが、reject counter である。このカウンタは coarse counter よりも reject\_count\_offset と呼ばれるオフセットを持って遅れて回っている。もし、L1 Buffer 内にあるエッジのそれぞれのカウンタの値が、この reject counter の持つカウンタの値に「抜かされる」と、そのエッジのデータは捨てられることになる。すなわち、reject\_count\_offset で設定した時間よりも古いデータはこのカウンタにより、自動的に捨てられるのである。これにより、古いヒットの情報がトリガーマッチングされることは防がれる。我々の用途では、reject\_count\_offset の値は  $30\mu$  sec に  $1\mu$ sec 程度のマージンをつけた程度に設定すれば良い。

また、常時ヒットを取り続ける場合についてであるが、その場合には  $30~\mu {

m sec}$  毎に AMT へと 強制的にトリガーを入れ続ければ良い。この場合、連続するトリガーでマッチングされる時間がわずかに重複するように設定しておけば、ヒットの取りこぼしを防ぐことができる。ただし、AMT は同じヒットを複数のトリガーで共有できてしまうので、重複したヒットを後で判別して除く必要 はある。

図 4.8 AMT におけるトリガーマッチング。matching\_window に入ったデータが Readout FIFO へと書き出される。reject counter のカウントより古いカウントは L1 Buffer から順次消されることになる。

AMT の処理速度 AMT に関する説明の最後に AMT の処理速度について述べておく。 AMT の処理速度に関しては [13] 中に表 4.5 のように述べられていて、AMT の全てのチャンネルに  $400~\rm kHz$  の入力があっても、AMT は損失無く処理できる。ただし、光電子増倍管の  $1~\rm Ly$

トにつき、AMT では立ち上がりと立ち下がりの両方のエッジを検出しなくてはならないから、実質的な速度は半分になり、AMT では全てのチャンネルに  $200~\mathrm{kHz}$  のヒットがあってもデータの損失は無視できるということになる。

したがって、AMT の処理速度は処理速度の要請に対しては十分速いと考えることができる。

表 4.5 AMT の処理速度

| データ損失が無視できる最大入力頻度      | 400  kHz/ch          |  |  |

|------------------------|----------------------|--|--|

|                        | 20 MHz (1 チャンネルのみ使用) |  |  |

| トリガーの損失が無視できる最大のトリガー頻度 | 200 kHz              |  |  |

#### 4.3.5 データ量と処理速度

それでは、QTC と TDC の速度やデータ構造などを理解したところで、新 ATM 全体のデータ量、処理速度の議論に移りたいと思う。

データ構造 まず、新しい ATM での 1 ヒットのデータ構造を表 4.6 に示す。現在の ATM と 比べて、扱うべきデータ量は増えているが、ワードごとの識別ビットを無くし、イベント番号や TDC のカウントなどは 2 つのワードに分けるなどして、現在の ATM と同じ 6 Byte に抑えた。

表 4.6 新 ATM の 1HIT あたりのデータ構造。現在の ATM と同じ 6 Byte である。(E は Event #の残り 1 ビット、TDC は TDC Count の残り 2 ビットである。Range は QTC のどのレンジを用いるかの識別のビットである。)

| 15  | 14                    | 13  | 12  | 11 | 10 | 09                    | 08 | 07   | 06    | 05 | 04 | 03 | 02 | 01 | 00 |

|-----|-----------------------|-----|-----|----|----|-----------------------|----|------|-------|----|----|----|----|----|----|

|     | Ch # (5bit)           |     |     |    |    | Event $\# (12-1)$ bit |    |      |       |    |    |    |    |    |    |

| Е   | TDC Count (17 – 2)bit |     |     |    |    |                       |    |      |       |    |    |    |    |    |    |

| TDC |                       | Rai | nge |    |    |                       | Q  | TC ( | 10 bi | t) |    |    |    | 0  | 0  |

FPGA でのデータ選別 TDC として AMT を用いることで時間測定のダイナミックレンジを拡大することはできたのだが、どんな事象に対してもこのような大きな時間幅で測定する必要は必ずしも無いのである。そもそも、 $30~\mu {

m sec}$  といった大きな時間幅を測定する必要があったのは、ミューオンの崩壊電子事象をより多く観測できるようにするということと、超新星残骸ニュートリノのバックグラウンドを効率的に除くためであった。したがって、 $10~{

m MeV}$  以下の低エネルギーの太陽ニュートリノ観測にとっては無駄なデータの量を増やしてしまっているだけに過ぎなくなってしまう。しかも、トリガーの頻度が最も大きいのはそうした低エネルギー事象であり、この方法は膨大な量の無駄なデータを生み出すことになってしまう。

図 4.9 トリガーの識別用に TDC の 3 つのチャンネルを使用する。それらのチャンネルのヒット情報から、トリガーの種類を知ることができる。

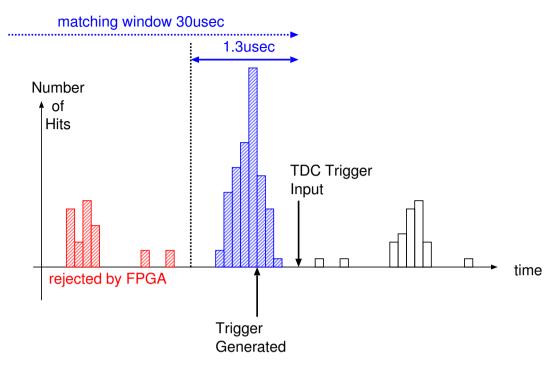

この無駄を減らすためにはトリガーの種類によって、データを取得する時間範囲を変えれば良い。ただし、TDC の設定をトリガーごとに変えるということは不可能である。TDC から出力されるデータは常に  $30~\mu sec$  の時間幅のデータを含むので、それを選別しなくてはいけないのは TDC とデータをやりとりする FPGA (DSM) である。このデータ選別のために Wide Window Trigger と Narrow Window Trigger という  $2~\sigma$ 0のトリガーを用意することにした。Narrow Window Trigger というのがデータの選別を行うトリガーである。これらのトリガーは Master Clock Module を通してクロックなどともに全ての ATM へと配られることになる。

それぞれのトリガーでの各部の動作は次のようになる。

- Wide Window Trigger (☒ 4.10)

- 1. Master Clock Module に Wide Window Trigger が入力されると約 15 $\mu$ sec の遅延をこのモジュールの内部で発生させる。その後、トリガーはシリアルで全ての ATM へと分配される。

- 2. FPGA はシリアルトリガーを受けて、TDC へとトリガーを入力する直前に、トリガー 識別のために TDC に一つ用意されているチャンネルに信号を入力する (図 4.9)。

- 3. その後、FPGA は TDC に対してトリガー信号を入力する。

- 4. 各チャンネルからのエッジ時間の情報とともに、トリガー識別用のチャンネルのヒット情報も TDC から読み出される。

- 5. Wide Window Trigger ではデータ選別の必要は無いから、全ての時間幅の情報を使う。

- Narrow Window Trigger (☒ 4.11)

- 1. Narrow Window Trigger の場合には、トリガー発生から TDC へのトリガー入力までにわざわざ遅延を発生させる必要は無い。したがって、Master Clock Module は Narrow Window Trigger が入力されたらできるだけ早く、シリアルトリガーを出力する。

- 2. FPGA がシリアルトリガーを受け取ると、FPGA は TDC ヘトリガー信号を入力する。(Wide Window Trigger と Narrow Window Trigger は互いに排他的なものであるから、この場合は TDC の識別チャンネルへの入力は必要無い。)

3. TDC からの各エッジの情報を受け取り、Wide Window Trigger の識別用のチャンネルに何も入力が無かったことを確認すると、FPGA では図 4.11 のように立ち上がりエッジの時間がトリガー入力の約  $1.3~\mu sec$  以前にあったヒットの情報を捨てる。

また、他にも Split Trigger と Pedestal Trigger というトリガーもある。Pedestal Trigger については文字通りペデスタルデータ取得用のトリガーである。一方、Split Trigger は外水槽の光電子増倍管からのデータが必要ないときにこのトリガーが入力される。各 ATM の FPGA では、それぞれ自らが内水槽を担当しているのか、外水槽を担当しているのかを認識しておき、外水槽を担当している ATM がこのトリガーを受け付けたときには、TDC からの全てのデータをそこで無視することになる。ただし、TDC へのトリガー入力はイベント番号がずれるのを防ぐためにこのときも行われる。

図 4.10 Wide Window Trigger のデータ取得範囲。この場合は TDC でトリガーマッチングされる範囲と同じである。

FPGA の処理速度 さて、問題は 4.3.1 の信号の流れで述べたような処理を FPGA がどれだけ の時間できるかである。FPGA に関してはまだ設計の途中であるので、現時点では概算された結果を示す。

例えば、1 イベント中に ATM の全てのチャンネルから 1 ヒットずつあった場合では、TDC がデータを出力し始めてから、SIC の転送バッファに書き込みが完了するまでにかかる時間は約 1.8  $\mu$ sec 程度である。したがって、基本的には FPGA は最大  $500~\mathrm{kHz}$  の処理速度を持つと言うこと

図 4.11 Narrow Window Trigger のデータ取得範囲。この場合には、TDC へのトリガー入力から  $1.3~\mu sec$  以前のデータは FPGA によって捨てられる。

#### ができる。

ATM 全体としての処理速度 それでは、最後に新しい ATM の全体としての処理速度についてまとめてみる。

表 4.7 は新 ATM の各部の最大での処理速度である。新しいエレクトロニクスへと要請されるスピードは全チャンネルで常時  $10~\mathrm{kHz}$  のヒットがあっても処理できることであったから、この要請に対しては ATM としては十分な処理速度を持っていると言うことができるだろう。

それでは、システム全体で  $10~\mathrm{kHz}$  という要請は、どのように実現されるのか、その詳細について次節で述べることにしよう。

表 4.7 ATM の各部の最大処理速度

| QTC  | 2 MHz/ch                   |

|------|----------------------------|

| AMT  | $\sim$ 200 kHz/ch          |

| FPGA | $\sim 500~\mathrm{kHz/ch}$ |

## 4.4 データ収集システム全体の高速化

ATM とオンライン計算機の間のデータ転送速度の高速化に関して、2 つの方法が考えられていることはもう既に述べた。ここでは、それらの詳細について述べていくこととする。

#### 4.4.1 新 SCH の開発と高速化 TKO プロトコル

新しい ATM でも TKO 規格を採用することにより、現在のシステムとの互換性は保たれる。しかし、TKO 自体が開発されてから既に 20 年が経ち、現在の水準から言えば、高速なデータ転送とは言えないものとなっており、互換性を保ちながらも、高速化が可能な方法を考える必要がある。

そこで、同じ TKO バスを使うにしても、バスサイクルにかかる時間を削減することで TKO バスの高速化ができないかと考えている。現在の各デバイスの性能を考えれば、これは無理のない変更であると考えられる。ただし、これは TKO プロトコルにおけるマスターである SCH とスレーブである ATM の両方がその変更に対応している必要がある。したがって、SCH を新しく開発することが必要となってくるのである。

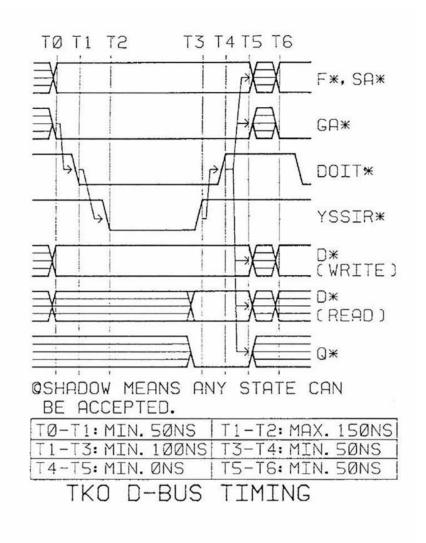

高速化 TKO プロトコル 標準の TKO プロトコルの D-Bus のタイミングチャートを図 4.12 に示す。例えば、SCH が ATM からデータを読み込むときには次のようなタイミングでハンドシェイクを行っている。書き込みのときもほぼ同様である。

- 1. TO SCH が GA (Geographical Addresses)、SA (Sub-Addresses)、F (Funtion) など の信号を有効にする

- 2. T1 SCH が DOIT\* 信号を Low にする

- 3. T2 ATM が YSSIR\* 信号を Low にする

- 4. T3 ATM が 16 ビットのデータバスにデータを出力して、YSSIR\* 信号を High に戻す

- 5. T4 SCH がデータの読み込みを終えたら、DOIT\* 信号を High に戻す

- 6. T6 次のデータ読み出しのために SCH が GA、SA、F などを有効にする

各段階で要する最小の時間は図 4.12 の中に記されており、1 サイクルの最小時間、すなわち、T0 から T6 までにかかる最小の時間は 250 nsec である。したがって、この標準 TKO プロトコルでの最大データ転送速度は 8 MB/sec である。ところが、現在の ATM では DOIT 信号を受け取ってから、データを出力するまでの時間 T1-T3 は 400 nsec 程度かかってしまっているので、実際のバスサイクルにかかる時間は最小で 550 nsec となる。ただし、これはあくまで最小値であり、実際にはさらに遅く、転送速度は 2 MB/sec 程度になってしまう。

そこで、高速化の第一段階としてはまず、ATM の応答時間を短くすることである。新しい ATM では、DOIT 信号から 2、3 クロックでデータを準備できるようにする予定である。これにより、T1-T3 の時間を 50 nsec 程度に短縮する。これにより、バスサイクルにかかる時間は現在の約 1/2 になるので、データ転送速度としては最大で約 4 MB/sec 程度となる。この段階では、まだプ

図 4.12 TKO の D-Bus タイミング [14]

ロトコル自体の変更はなく、ATM を新しくするだけで 2 倍程度の高速化は望めるということである。

次に、高速化 TKO プロトコルについてであるが、現在のプロトコルでは、SCH と ATM 間の ハンドシェイクのある部分でのマージンが 50 nsec とられている。この時間は十分過ぎるほど長いものであり、半分の長さの 25 nsec でも問題なく動作するものを作ることは可能であると考えられる。このようにした場合のバスサイクルの時間は表 4.8 の右側の列にまとめられている。こうした場合、1 サイクルの時間は 125 nsec 程度になる。したがって、最大のデータ転送速度は 16 MB/sec となる。この 25 nsec というマージンについては技術的には特に厳しい要求でもないのだが、SCH 側もそのマージンを前提に動作する必要があるので、このプロトコルを採用する場合には、SCH 側も新しく開発する必要があるのである。

表  $4.8~{

m TKO}$  プロトコルの各段階に要する時間。現在の  ${

m ATM}$  と新しい  ${

m ATM}$  の場合、また、 ${

m SCH}$  も新しくした場合の 3 通りについてまとめた。

|         | Current ATM              | New ATM                 |                          |  |  |

|---------|--------------------------|-------------------------|--------------------------|--|--|

|         | Current                  | SCH                     | New SCH                  |  |  |

| T0 - T1 | 50 nsec $\sim$           | $50~\mathrm{nsec}\sim$  | $\sim 25~\mathrm{nsec}$  |  |  |

| T1 - T3 | $\sim 400~\mathrm{nsec}$ | $\sim 50~\mathrm{nsec}$ | $\sim 50~\mathrm{nsec}$  |  |  |

| T3 - T4 | 50 nsec $\sim$           | $50~\mathrm{nsec}\sim$  | $\sim 25~\mathrm{nsec}$  |  |  |

| T4 - T6 | 50 nsec $\sim$           | 50 nsec $\sim$          | $\sim 25~\mathrm{nsec}$  |  |  |

| 1 Cycle | 550 nsec $\sim$          | 200 nsec $\sim$         | $\sim 125~\mathrm{nsec}$ |  |  |

#### 4.4.2 イーサネット読み出しのための拡張ボード

データ転送の高速化のもう一つの方法として、イーサネット読み出しという方法がある。これは、新 ATM に拡張ボードをつけて、その拡張ボードから 100BASE-T のイーサネットで読み出すという方法である。

$100 \mathrm{BASE-T}$  の実効速度としては、 $5~\mathrm{MB/sec}$  程度であると考えられるから、この場合にも拡張ボードと ATM の間のデータのやりとりは高速化 TKO プロトコルで十分である。したがって、このボードでは一方では、TKO プロトコルで ATM とデータのやりとりをし、もう一方では、TCP/IP プロトコルでオンライン計算機とデータのやりとりをすることになる。

## 4.4.3 高速化に関するまとめ

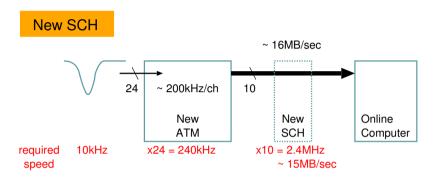

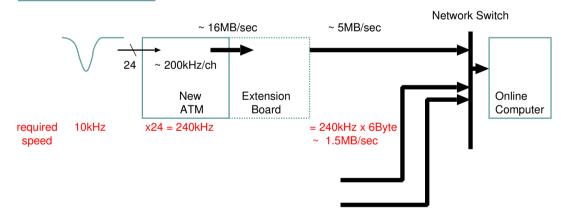

以上に述べた 2 つの方法で要請される速度が実現されるのかを確かめてみる。図 4.13 に新しいシステムでの ATM からオンライン計算機までのデータ転送速度を示す。

新しい SCH を開発した場合は、一つの SCH で 240 チャンネルの信号を処理しなくてはいけない。それぞれのチャンネルから 10 kHz のヒットがあった場合、一つの SCH で処理すべきヒットは 2.4 MHz 、すなわち、データ量にして 15 MB/sec である。一方、高速化 TKO プロトコルの最大速度は 16 MB/sec であるから、マージンは少ないが基準は達せられていると言える。

また、各 ATM から拡張ボード経由でイーサネット読み出しをする場合、この場合は ATM 一枚 一枚がオンライン計算機へとつながるから、ここで要請される速度は 24 チャンネル分の 240 kHz のヒット、すなわち、1.5 MB/sec である。一方、100BASE-T イーサネットでは 5 MB/sec 程度 の速度は出ると考えられるから、この部分は問題なく転送できると考えられる。ただし、この場合 もオンライン計算機は 1 クレートに 1 台程度であると考えられ、結局は 10 台程度の ATM と 1 台のオンライン計算機がつながることになるのだが、この場合はオンライン計算機側だけはギガビットのイーサネットで通信できるようなネットワークスイッチなどを用いることになると考えられる。そうすることで、要請される処理速度は問題なく満たすことができる。

以上から、どちらの方法でも、常時全てのチャンネルからの 10 kHz のヒットを取得するという 我々の処理速度への要請は満たすことができると言うことが分かった。ただし、イーサネット読み 出しの方が速度には余裕ができると考えられるから、開発に問題が無ければ、こちらの方法を採用 する方が好ましい。また、オンライン計算機へと転送した後の計算機での処理に関してはここでは 全く議論してこなかった。この部分の議論は始まったばかりであるが、同程度のデータ量を扱うシ ステムは大規模な加速器実験では既に構築されているものもあり、実現は十分可能であると考えて いる。

## **Ethernet Readout**

図 4.13 新しいシステムでの ATM からオンライン計算機までの処理速度

#### 4.5 トリガーシステム

新しいシステムでは、トリガーの改良も求められる。そのうち、トリガーをシリアル化して全ての ATM へとトリガーの種類の情報を分配することは述べた。ここでは、トリガーの生成に関するこの改良について述べる。

ただし、常時データを取り続けるようなシステムにした場合には、ここでいう、トリガーは殆ど意味をなさなくなると考えられるから、ここで述べられるシステムとも全く違うものとなると考えられる。そのときには、トリガーとは、オンライン計算機でなされる"Intelligent Trigger"のことをいうことになるのだろう。

## 4.5.1 Forced Trigger

新しい ATM では AMT という TDC を用いることで、時間の測定範囲をトリガーの生成から 前後の  $15~\mu {

m sec}$  に拡大することができたということを述べた。しかし、時間の測定範囲に関しては もう一つ要請があり、それは、超新星残骸ニュートリノ観測のために約  $200~\mu {

m sec}$  後に放出される  $2.2~{

m MeV}$  の  $\gamma$  線を観測するということであった。そのような長い時間幅は、AMT でも取得できないが、常時ヒットをとるのと同じように、 $200~\mu {

m sec}$  の間の信号を取るためには、その間強制的 にトリガーを入れ続けてやれば良いことは簡単に分かる。

このためには TRG の直前の現在のトリガー生成ロジックに置き換わる、もしくは、加えられるようなモジュールを開発する必要がある。このモジュールは、超新星残骸ニュートリノの観測領域である、 $10~{

m MeV}$  以上に相当するヒットがあったときにそれから数  $100~{

m \mu sec}$  の間に渡って、強制トリガーを出力し続ける。

#### 4.5.2 Digital HITSUM

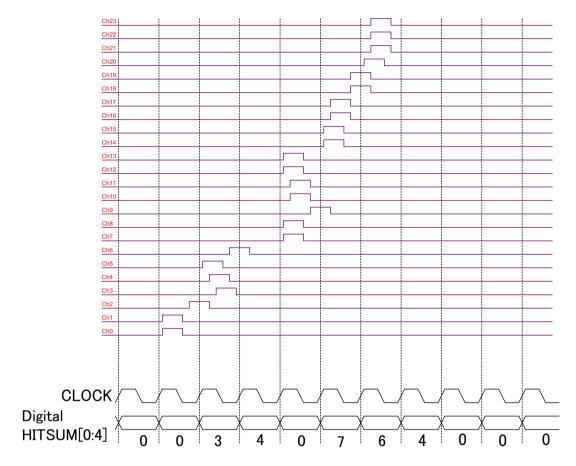

新しい ATM では、ヒット信号の外部への出力方法が 3 種類も用意されている。一つは現在のシステムと全く同じで、 1 ヒットにつき -15 mV の 200 nsec 幅の信号のアナログ和、二つめはそれをデジタル化したもの、最後の一つは全てのヒットの信号を別々に外部へと出力するものである。

ここでは、そのなかの二つめの Digital HITSUM について説明することにする。これは、一枚の ATM ボードのなかで 1 クロックの間にいくつのチャンネルでヒットがあったかを FPGA で数えて、それを 5 ビットの信号で出力するものである。図 4.14 がその例である。図 4.14 中では、ヒットのあった 1 クロック後にすぐに Digital HITSUM 信号にその数が出力されているが、実際は同期化や加算などを行うことにより、5、6 クロック分ぐらいの遅延が生じると考えられる。

これらの信号はセントラルハットへと集められ、アナログ信号による HITSUM と同様に全てのチャンネルでのヒット数の和からグローバルなトリガーが生成される。この方式が、アナログ信号より優れている点は、アナログ信号では各 ATM ボードの HITSUM 信号の幅や振幅のばらつきにより、HITSUM のなかでの重みが少しずつばらついてしまうと言うことも考えられるのだが、デ

ジタル信号で処理すればそのようなことは起こらず、全てのチャンネルのヒットを平等に扱うこと ができるのである。

☑ 4.14 Digital HITSUM

# 5 時間電荷変換素子 (QTC-LSI) の研究と開発

この章では、新 ATM における AD 変換において中心的な役割を果たす時間電荷変換素子 (QTC) の開発について述べる。以下では、既に完成しているプロトタイプについて、仕様の検討 及びプロトタイプ完成後の性能評価、さらには、次期版の開発について述べることになる。

## 5.1 QTC への要請と仕様の検討

最初に、QTC への要請とそれに応えるための仕様の検討について述べる。

まず、ATM への要請のうちいくつかは QTC への要請となって残されたままである。それらについて確認のため、繰り返しになるが QTC への要請を述べておく。

- 1.1% の電荷測定(相対)精度

- 2. 20 インチ光電子増倍管より十分良い時間測定精度

- 3. 2500 pC までの電荷測定のダイナミックレンジの拡大

- 4. AD 変換の高速化

- 5. 高精度のインピーダンス整合

- 6. 低ノイズ化 (ディスクリミネータ閾値  $\rightarrow -0.5 \text{ mV}$ )

- 7. 低消費電力化

- 8. キャリブレーション作業の簡素化

これらのことを念頭に、仕様に関する議論をしていくこととする。

#### 5.1.1 電荷分解能とダイナミックレンジ

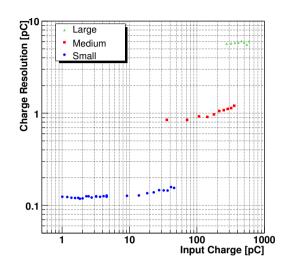

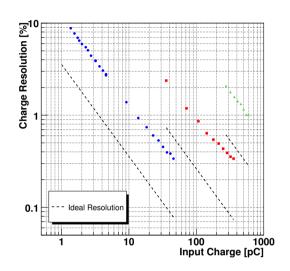

電荷分解能に対する要請としてはすべてのレンジに渡って測定電荷に対する相対精度を 1~%以下に抑えることが求められる。また、 $1~\mathrm{p.e.}$  レベルでの十分な相対精度を得るためには  $0.1~\mathrm{pC/Count}$  の分解能が必要である。さらに、電荷測定のダイナミックレンジとしては  $1000~\mathrm{p.e.}$ (  $\sim 2500~\mathrm{pC}$ ) 程度を要求される。

以上のような条件を同時に満たすために一つのチャンネルに対して 3 つのレンジを用意することにした。それでは、この 3 つのレンジのゲインをどのような比で分け、さらにそれぞれのレンジでは何ビットの分解能が必要となるであろうか。

まず、この 3 つのレンジを、それぞれ測定する電荷の大きさから Small, Medium, Large と呼ぶことににする。それぞれのレンジのゲインの比を n とすれば、最大測定電荷の比は  $1:n:n^2$  となるとする。また、このときのそれぞれのレンジにおける分解能(ダイナミックレンジ)を m ビットとする。最初に相対精度を 1 % 以下に抑えるという条件について考える。最も厳しい条件となるのは、そのレンジにおける測定範囲の最小の電荷を測定するときの相対精度である。例えば、Large レンジでは、最小の測定電荷は 2500/n [pC] であり、そのときの分解能 (LSB) は  $2500/2^m$

[pC/Count] となる。量子化誤差のみを考えた場合には測定精度は分解能の  $1/\sqrt{12}$  になるから、次のような条件が成り立てば良い。

$$\left(\frac{2500}{n}\right) \div \left(\frac{2500}{2^m \cdot \sqrt{12}}\right) \lesssim 0.01\tag{5.1}$$

次に Small レンジでの最大測定電荷は  $2500/n^2$  であるから、Small レンジでの電荷分解能が  $0.1~\mathrm{pC}$  以下となる条件は以下のようになる。

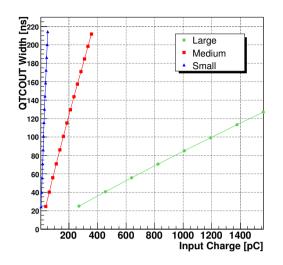

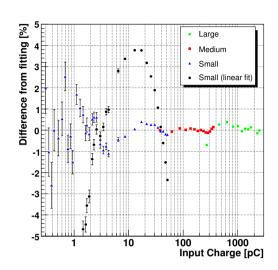

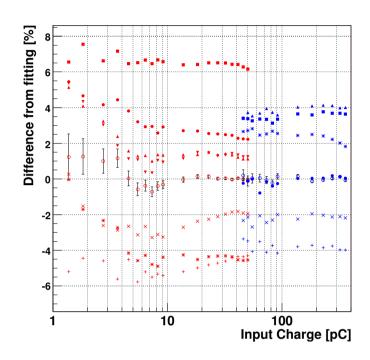

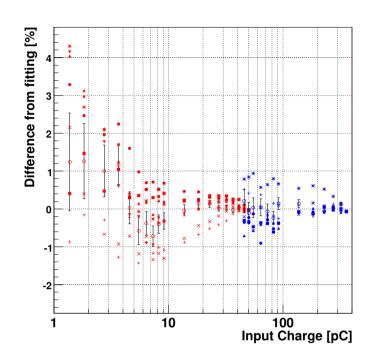

$$\frac{2500}{n^2} \frac{1}{2^m} \lesssim 0.1 \tag{5.2}$$